PCB的布线原则介绍

3. 信号走线

3.1 Modem信号走线中,易产生噪声的信号线和易受干扰的信号线尽量远离,如无法避免时要用中性信号线隔离。

Modem易产生噪声的信号引脚、中性信号引脚、易受干扰的信号引脚如下表所示:

3.2 数字信号走线尽量放置在数字信号布线区域内;

模拟信号走线尽量放置在模拟信号布线区域内;

(可预先放置隔离走线加以限定,以防走线布出布线区域)

数字信号走线和模拟信号走线垂直以减小交叉耦合。

3.3 使用隔离走线(通常为地)将模拟信号走线限定在模拟信号布线区域。

a) 模拟区隔离地走线环绕模拟信号布线区域布在PCB板两面,线宽50-100mil;

b) 数字区隔离地走线环绕数字信号布线区域布在PCB板两面,线宽50-100mil,其中一面PCB板边应布200mil宽度。

3.4 并行总线接口信号走线线宽>10mil(一般为12-15mil),如/HCS、/HRD、/HWT、/RESET。

3.5 模拟信号走线线宽>10mil(一般为12-15mil),如MICM、MICV、SPKV、VC、VREF、TXA1、TXA2、RXA、TELIN、TELOUT。

3.6 所有其它信号走线尽量宽,线宽>5mil(一般为 10mil),元器件间走线尽量短(放置器件时应预先考虑)。

3.7 旁路电容到相应IC的走线线宽>25mil,并尽量避免使用过孔。

3.8 通过不同区域的信号线(如典型的低速控制/状态信号)应在一点(首选)或两点通过隔离地线。如果走线只位於一面, 隔离地线可走到PCB的另一面以跳过信号走线而保持连续。

3.9 高频信号走线避免使用90度角弯转,应使用平滑圆弧或45度角。

3.10 高频信号走线应减少使用过孔连接。

3.11 所有信号走线远离晶振电路。

3.12 对高频信号走线应采用单一连续走线,避免出现从一点延伸出几段走线的情况。

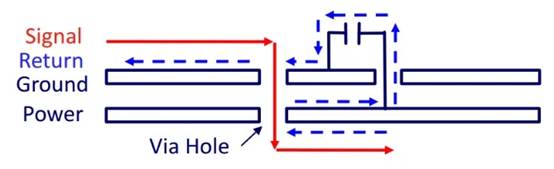

3.13 DAA电路中,穿孔周围(所有层面)留出至少60mil的空间。

3.14 清除地线环路,以防意外电流回馈影响电源。

4. 电源

4.1 确定电源连接关系。

4.2 数字信号布线区域中,用10uF电解电容或钽电容与0.1uF瓷片电容并联後接在电源/地之间。在PCB板电源入口端和最远端各放置一处,以防电源尖峰脉冲引发的噪声干扰。

4.3 对双面板,在用电电路相同层面中,用两边线宽为 200mil的电源走线环绕该电路。(另一面须用数字地做相同处理)

4.4 一般地,先布电源走线,再布信号走线。

5. 地

5.1双面板中,数字和模拟元器件(除DAA)周围及下方未使用之区域用数字地或模拟地区域填充,各层面同类地区域连接在一起,不同层面同类地区域通过多个过孔相连:Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.2 四层板中,使用数字和模拟地区域覆盖数字和模拟元器件(除DAA);Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.3 如设计中须EMI过滤器,应在接口插座端预留一定空间,绝大多数EMI器件(Bead/电容)均可放置在该区域;未使用之区域用地区域填充,如有屏蔽外壳也须与之相连。

5.4 每个功能模块电源应分开。功能模块可分为:并行总线接口、显示、数字电路(SRAM、EPROM、Modem)和DAA等,每个功能模块的电源/地只能在电源/地的源点相连。

5.5 对串行DTE模块,使用去耦电容减少电源耦合,对电话线也可做相同处理。

5.6 地线通过一点相连,如可能,使用Bead;如抑制EMI需要,允许地线在其它地方相连。

5.7 所有地线走线尽量宽,25-50mil。

5.8 所有IC电源/地间的电容走线尽量短,并不要使用过孔。

6. 晶振电路

6.1 所有连到晶振输入/输出端(如XTLI、XTLO)的走线尽量短,以减少噪声干扰及分布电容对Crystal的影响。XTLO走线尽量短,且弯转角度不小於45度。(因XTLO连接至上升时间快,大电流之驱动器)

6.2 双面板中没有地线层,晶振电容地线应使用尽量宽的短线连接至器件上离晶振最近的DGND引脚,且尽量减少过孔。

6.3 如可能,晶振外壳接地。

6.4 在XTLO引脚与晶振/电容节点处接一个100 Ohm电阻。

6.5 晶振电容的地直接连接至 Modem的GND引脚,不要使用地线区域或地线走线来连接电容和Modem的GND引脚。

模拟信号相关文章:什么是模拟信号

晶振相关文章:晶振原理

评论