基于DSP+FPGA汽车防撞报警设备高速数据采集

本系统在设计中DSP主要是通过C6713器件的外部存储器接口EMIF与FPGA进行数据通信。外部存储器接口(EMIF)是TMS DSP器件上的一种接口。一般来说,EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM等)的连接。用EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

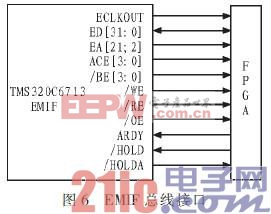

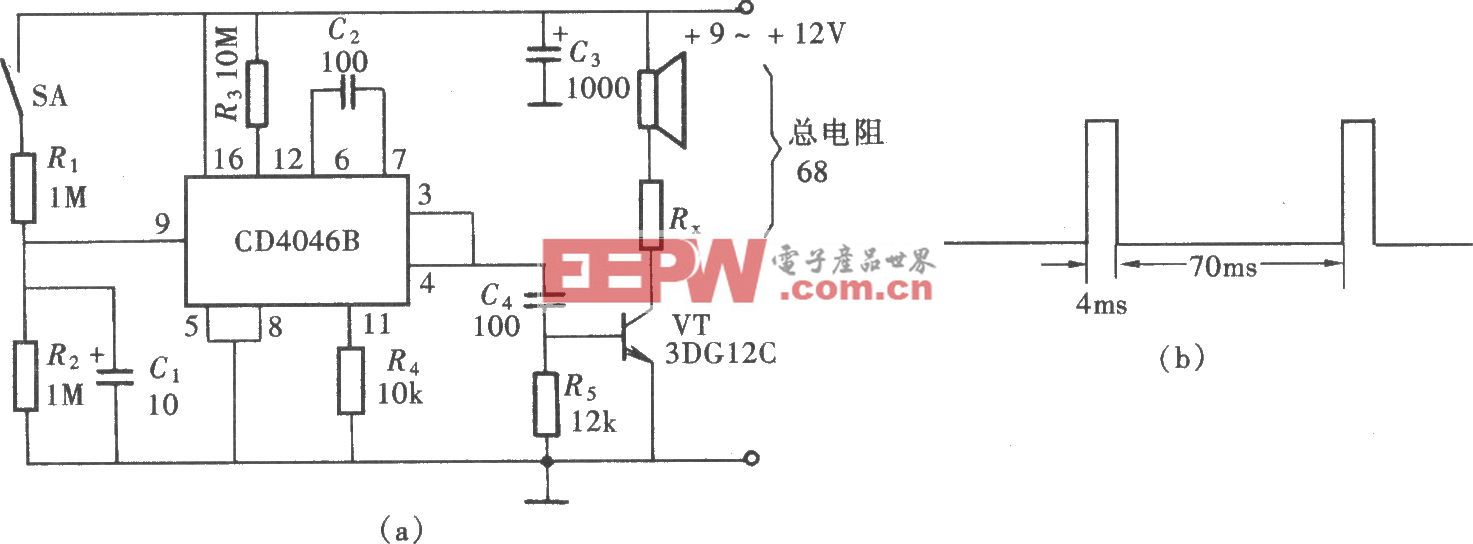

其EMIF的总线接口图如图6所示。

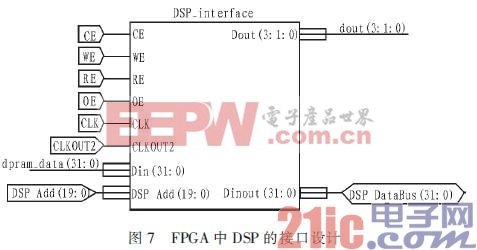

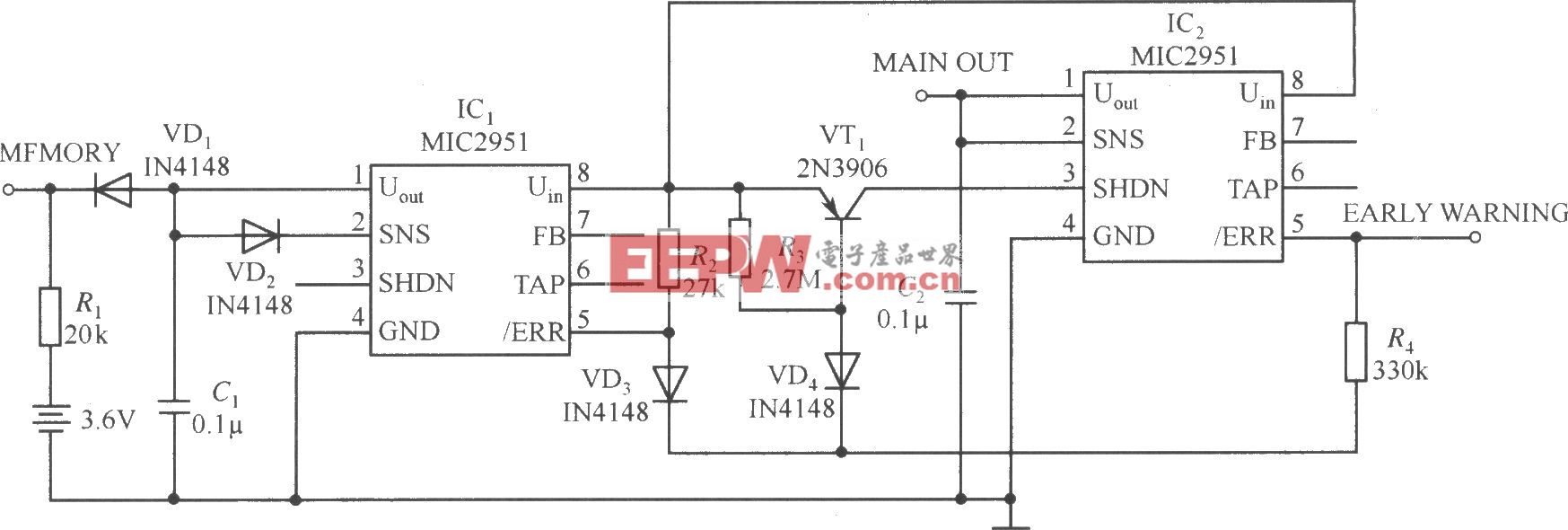

在完成对EMIF的DSP配置后,接下来就是实现EMIF接口的FPGA配置工作,保证FPGA中的数据正常的读入到DSP中。在FPGA中配置EMIF接口的连接图如图7所示。

该模块是DSP与FPGA进行通信的接口模块。通过该模块,DSP可以实现向FPGA传输控制信号,FPGA也可以通过该模块将FIFO中的数据传给DSP。CE、WE、RE、OE为DSP输入的使能信号,CLK为FPGA提供内部时钟,CLKOUT2是EMIF的输出时钟,为DSP与FPGA通信提供时钟频率,DSP_Addr(19:0)为DSP的输入地址,DSP_DataBus(31:0)为DSP的数据总线。FPGA根据读使能信号OE与片选信号CE的输入逻辑来判断EMIF是进行读操作还是写操作。当DSP通过EMIF读取数据时,FPGA中的数据从dpram_data(31:0)输入,由DSP_DataBus(31:0)管脚传送给DSP;若写数据,将DSP_DataBus(31:0)传来的数据从dout(31:0)送入FPGA。

2.4 人机交互模块

人机交互模块分为按健电路和LCD显示电路。限于篇幅,本文仅介绍LCD电路。

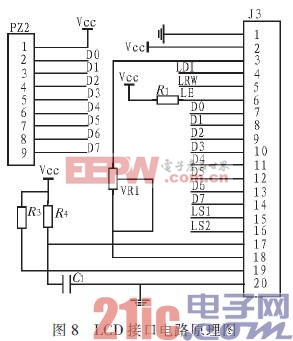

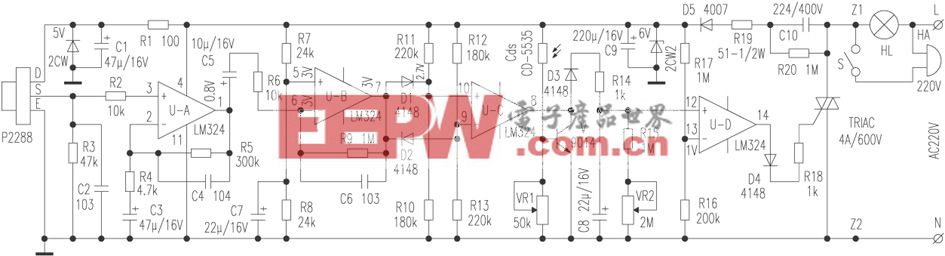

LCD显示部分我们采用真空荧光显示点阵式VFD屏,其优点是能高亮度发光。由于我们选择的屏是5 V供电,所以由DSP过来的3.3 V的信号线需要经过74LVCA245转化为5 V,再与VFD屏的控制器接口相连,LCD控制器接口如图8所示。

fpga相关文章:fpga是什么

评论