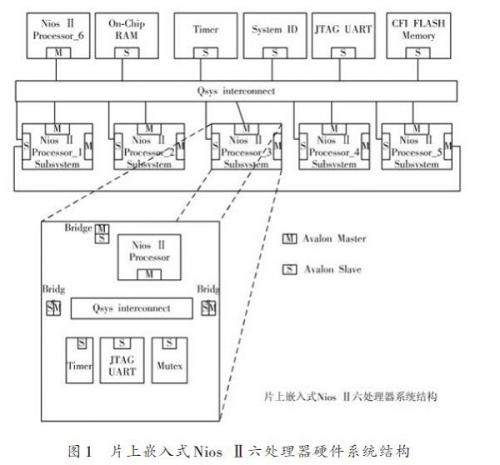

基于NiosⅡ的U盘安全控制器设计

2 安全控制器硬件架构的设计实现

本设计采用USB接口芯片+FPGA的方案来实现安全控制器的硬件架构,通过微处理器器对USB接口芯片的控制即可实现USB通信。采用USB接口芯片有助于降低开发费用,缩短系统的开发周期。

2.1 USB接口芯片选型

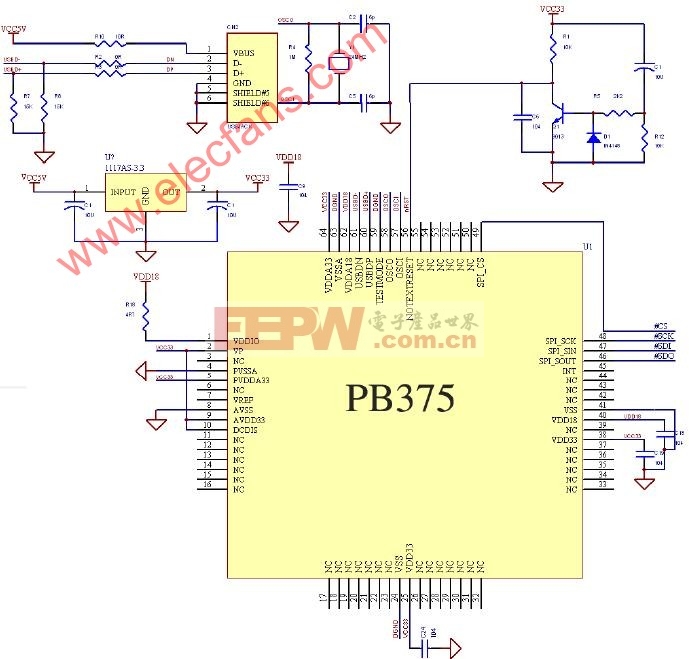

本设计中,安全控制器既要实现USB Host的功能,又要实现USB Device的功能。因此,若能采用一片USB接口芯片实现两者的功能,则有助于降低硬件系统的复杂性。综合USB芯片的功能需求、价格、硬件复杂性等因素,本设计选用NXP公司的ISP1761作为USB接口芯片。

ISP1761是一个单芯片的高速USB OTG 控制器,在其单芯片上集成了一个OTG控制器、一个主机控制器和一个外设控制器,主机和外设控制器兼容USB2.0协议,并支持480 Mb/s的高速传输。ISP1761有3个USB接口,接口1可以被配置为Host接口、Device接口或者OTG接口,接口2、3只能被配置为Host接口。在OTG模式下,ISP1761的接口1可通过跳线灵活配置成Host接口或Device接口。ISP1761可以直接与目前市场上的大多数带寻址功能的微处理器直接连接,微处理器通过读写ISP1761内部的寄存器或存储器即可实现USB通信功能。ISP1761支持DMA传输,可以提高数据的吞吐率[4]。

2.2 控制器整体硬件架构

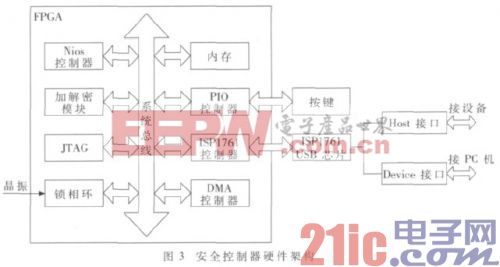

安全控制器整体硬件架构如图3所示,由SoPC模块和ISP1761芯片及按键组成。SoPC模块使用Altera公司提供的开发工具SoPC Builder生成,主要由NiosⅡ控制器、内存、加解密模块、JTAG、ISP1761控制器、锁相环、PIO控制器和DMA控制器组成。

NiosⅡ控制器作为整个系统的核心,完成对各个模块的调度和控制;锁相环为系统各个模块提供所需要的时钟;加解密模块完成数据流的加解密功能;ISP1761控制器则用来连接NiosⅡ控制器和ISP1761芯片,通过该控制器,NiosⅡ处理器可以访问ISP1761芯片内部的寄存器和存储器;DMA控制器负责PC机到控制器、控制器到U盘的数据传输,提高数据传输速率。ISP1761芯片分别连接主机和U盘,在NiosⅡ的控制下实现USB Host接口和USB Device接口的功能。

3 安全控制器固件的设计实现

3.1 固件模块及层次的划分

安全控制器固件实际上是运行于NiosⅡ处理器上的COS(Chip Operating System),主要负责监控USB Host接口及USB Device接口的状态,解析PC机发出的命令,对系统各个模块进行调度,实现PC机到U盘间的数据通信,完成数据流的加解密。

安全控制器固件主要包括初始化模块、USB Host模块、USB Device模块、DMA模块、密码模块等。各模块的功能如下:

(1)初始化模块:安全控制器系统的启动;ISP1761芯片接口的配置,将接口1配置成USB Host接口,接口2配置成USB Device接口。

(2)USB Host模块[5]:检测USB接口芯片Host接口的状态,检测U盘的插入和移除等;向插入的USB设备发出标准的USB标准命令,获取设备描述符、配置描述符、接口描述符、端点描述符等;向插入的USB设备发出USB MassStorage类命令,获取设备的容量等基本信息及对设备进行读写操作。

(3)USB Device模块:向PC机报告USB设备的插入;响应PC机发出的标准的USB命令,返回相应的数据,如各种描述符等。此时返回的描述符应为安全控制器的描述符;响应PC机发出的USB MassStorage命令,返回设备的基本信息,此时返回的基本信息应为U盘的信息。

(4)加解密模块[6]:身份认证方案的实现,如用户口令的保存、更改等;加解密算法的高速实现及密钥的保护等。

(5)DMA模块:DMA控制器的配置、启动等。

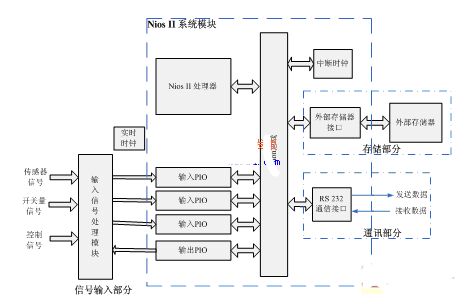

安全控制器固件层次划分如图4所示,主要包括硬件抽象层、USB协议层和批量传输层。硬件抽象层主要实现NiosⅡ处理器对外设的读写以及对ISP1761芯片内部寄存器和存储器的访问;USB协议层通过对ISP1761芯片的控制实现USB协议;批量传输层则实现MassStorage类的操作,通过Bulk-In和Bulk-Out端点,完成CBW、数据、CSW的传输。安全控制器在批量传输层对数据进行扇区级的加解密操作,不进行文件系统级的解析。

评论