基于FPGA的DDR2 SDRAM存储器用户接口设计

接口控制模块主要是接收写通路的写操作请求信号以及它对应的地址信号和数据信号,读通路的读操作请求信号以及它对应的地址信号,并将这些信号按照DDR2存储控制器的时序要求发送给DDR2存储控制器,之后再接收DDR2存储控制器发回的读数据。DDR2存储控制器的读写操作时序如图3所示。本文引用地址:http://www.eepw.com.cn/article/189601.htm

3 仿真验证

对本设计的验证采用的是6路8位数据以27 MHz的频率写入读出操作。对其进行整体读写仿真的时序结果如图4所示。

由该图可知,当将数据写入到DDR2中的数量到达一定程度时,开始向向外读出数据,写入的时序和读出的时序整体上符合设计要求。

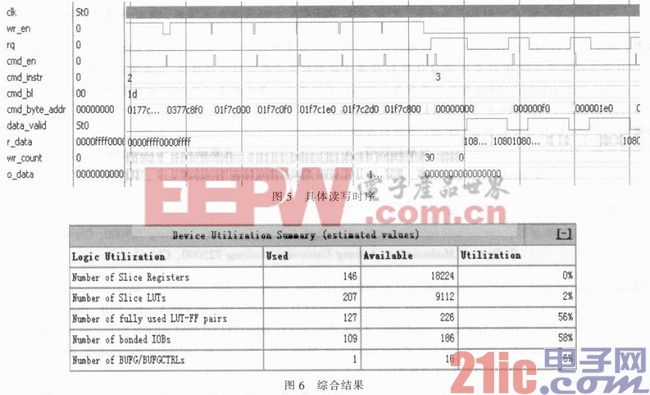

对读写操作的具体仿真时序如图5所示。

由该图可知,写操作时的各种控制指令以及地址和数据的发送都是完全正确的;读操作时的各种控制指令以及地址和数据的发送也是完全正确的。

对该设计采用XILINX Spartan6系列的xc6slx16—2ftg256器件进行综合,其结果如图6所示。

由该图可知该设计使用的逻辑资源相当小,其中寄存器还不到总数的百分之一,查找表也只使用了总数的百分之二。

4 改进

在一般情况下,DDR2的硬件存储速率很快,其会等待存储控制器发送下一个操作指令,而DDR2存储控制器的操作指令是由用户接口发出的,因此可以提出以下改进方案。可以在存储控制器前端添加多个FIFO,将与操作有关的所有指令、地址以及数据对应起来存入这些FIFO中,这样等到DDR2存储控制器将本次操作完成之后自动将所有FIFO中与下次操作有关的指令和数据读出,直接进行下一次DDR2的操作,与此同时用户接口部分在这些FIFO没满的情况下,还仍然向这些FIFO中写入要操作的所有指令和数据。

5 结论

由以上仿真结果可知,该设计在整个设计读写频率很高时仍然可以保证所有数据的正确操作,不会存在数据的丢失或者错误。由以上综合结果可知,该设计占用的FPGA片上资源很少,运行频率很高,基本可以满足所有设计的要求。因此可知,该设计具有很高的工作频率,解决了电路设计中DDR2存储器读写操作频率的瓶颈问题,使得整个设计的工作效率得到很大的提高。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论