如何用FPGA构建便携式超声系统?

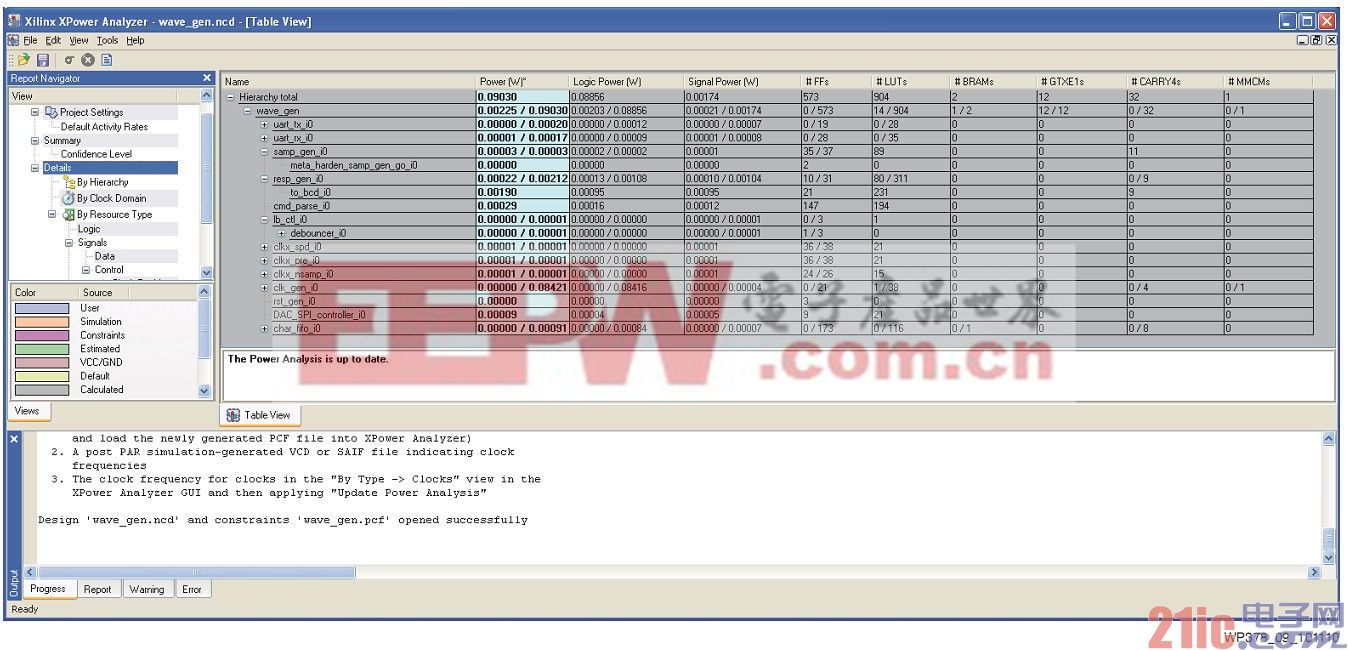

赛灵思独特的自动时钟门控技术能将动态功耗降低多达30%。下一步重要工作就是用赛灵思的XPower Analyzer全面分析设计功耗情况,如图9所示。

图9 XPower Power分析界面

该工具可提供准确的实现后功耗分析,凸显了潜在能够降低功耗的设计区域。根据功耗瓶颈情况,用户能够实现赛灵思自动化功耗改进工具的任意组合,如逻辑再综合、功耗优化放置以及路由电容优化等。如果仍需要进一步降低功耗,我们还能用XPower工具来明确哪些模块产生的功耗最多,哪些设计方法最适用于降低动态功耗。

采用赛灵思FPGA从容应对接口挑战

便携式超声系统中最关键的接口瓶颈是AFE到波束形成器的接口,我们在此需要大量I/O与并行DAC和LVDSADC接口相连。

为了进一步降低AFE到波束形成器接口的复杂性,模拟供应商采用高速串行JEDEC JESD204A标准作为从ADC向DAC传输数据的高效途径,其速率可高达每通道每秒3.125Gb。赛灵思能够为采用GTP/GTX收发器的ESD204A标准提供全方位的支持。

虽然JESD204A标准是比较受青睐的解决方案,但在多个低逻辑密度的高引脚数FPGA上对前端设计进行分区更合适。这种方案几乎彻底杜绝了在以下方面同时进行输出(SSO)转换的问题,如:在更多VCC/GND对上分布I/O;为PCB布局工程师提供更大的工作面积(这可进一步避免PCB路由拥堵问题),以及;为在更大的封装和PCB空间(可作为散热片发挥作用)中进行布局设计减少了散热管理问题。不过,设计分区也会带来PCB尺寸放大的不利影响,进而导致系统体积增大,因此设计人员应当根据空间约束、通道数量以及模拟前端的设计要求实现良好的平衡。

在此情况下,FPGA可谓最佳解决方案,能实现较多的引脚数量,同时还具有大容量的片上存储器。

可高度扩展的设计

如果采用7系列FPGA的统一架构,就能大幅缩短开发时间,确保用户快速在整个产品系列中实现设计模块的移植。此外,IP核的可用性也能显著获得提升,因为赛灵思和IP核合作伙伴仅需一次性优化IP核即可,随后就能根据不同的器件要求加以调整,从而尽可能减少修改幅度,而且每个系列的重复验证也会很方便。统一架构的另一优势在于其能在较短的时间内为新的超生系统获得医疗设备认证,因为大部分HDL代码都能在不同产品系列上实现重复利用,在某些情况下甚至包括网表的重复利用。

总而言之,赛灵思的通用架构能大幅提高超声系统供应商的规模经济效益,帮助他们提供多种不同的系统功能和复杂性选择,同时还能缩短开发时间和产品的批准认证时间,使供应商能够更方便地根据不同应用需求使用性价比最高的器件。

赛灵思IP核

赛灵思IP核是赛灵思设计方案的关键构建块。种类丰富的基础IP核可满足FPGA设计人员的一般性需求,而稳健可靠的特定领域和特定市场IP核则能满足DSP、嵌入式和连接设计的特定需求。超声系统所需的众多关键DSP功能和连接接口都可作为赛灵思或合作伙伴的IP核提供。使用赛灵思IP核不仅能够最大限度地缩短开发时间,并且还能帮助用户集中精力实现产品差异化设计,而非标准功能开发——这是使用赛灵思产品的一项独到的优势。

总结

Spartan-6、Virtex-6和7系列FPGA均可提供专用ASIC和DSP的高性能,同时还具备极低NRE成本、大幅缩短产品上市时间、便于设计移植、高I/O数量和PCB布局简化等优势。此外,配合业界领先的功耗优化工具,赛灵思的40nm和即将推出的28nmFPGA定制低功耗工艺技术还能大幅降低功耗,显著优于业界同类型的竞争解决方案。上述所有优势都能帮助便携式超声系统开发人员快速部署系统,在预算和功耗要求限度内推出最新技术,从而改进患者的护理工作。

fpga相关文章:fpga是什么

模数转换器相关文章:模数转换器工作原理

评论