如何用FPGA构建便携式超声系统?

波束形成器

超声波束形成器包括两个组成部分。发射波束形成器(又称Tx波束形成器)负责启动扫描线并生成发送给换能器元件的定时脉冲串,以设置对象所需的聚焦点。接收波束形成器(又称Rx波束形成器)负责从模拟前端接收回波波形数据,并将数据通过滤波、开窗(切趾术)、求和及解调整理为代表性扫描线。这两个波束形成器模块保持时间同步,连续向彼此传送时序、位置和控制数据。

Tx波束形成器负责定时数字脉冲串的导向(steering)和生成,该脉冲串外部转换为换能器的高压脉冲。根据给定扫描线聚焦超声波束所需的即时位置可实时计算出延迟。Tx波束形成器模块相当小,占用的逻辑资源不到Rx波束形成器的10%。其包括时序生成器和脉冲成形,通常并行连接到外部DAC。

Rx波束形成器对原始换能器Rx数据进行分析,以提取并聚集成超声扫描线。这是一个DSP密集型模块,会占用大量的逻辑资源。图6对处理步骤和子模块进行了汇总。

图6 Rx波束形成器功能步骤

每个通道都要进行上述每个步骤,直到最后求和;而每个扫描线则需要进行其他步骤。这是一种典型的处理流程,实际超声实施方案可采用上述步骤的任意组合,并配合其他专有处理模块。

后端处理

后端处理引擎通常包括B模、M模、多普勒和彩色血流处理功能块。上述功能块同时工作,执行多种不同的任务。B模处理引擎负责接收解调和压缩的扫描线,并用内插和灰度映射在扫描线基础上形成二维灰度图像。M模将一段时间内的数据点加以比较,从而识别出声源的运动、速度和运动位置。多普勒处理来自多普勒专用模拟前端的数据,并生成精确的方向和速度信息。彩色血流处理模块将色度映射到运动数据上,反映出速度和方向,再将其覆盖到B模功能块生成的灰度图上。随后后端进行清空,根据超声医师和所用显示设备的要求调节图像,并存储、显示和发送静态输出及视频输出。

我们可在超声系统中使用多种不同增强技术来减少斑点,改进聚焦,并设置对比度和灰度深度。例如:角复合、小波分解、各向异性双边滤波、直方图均衡化、帧平滑、边缘检测等。

功耗

降低功耗是一项主要的设计约束。就便携式医疗超声系统而言,降低功耗至关重要。医疗系统电源对安全性和质量也有着严格的标准要求。在满足上述安全性和质量标准要求的同时,一旦对功率要求有所提升,电源设计必将面临非常严峻的成本和复杂性挑战。

散热也是降低功耗的一大原因。必须做好散热工作,确保系统组件的温度在适当的工作范围内。因此我们必须认真设计散热片、风扇、封装和PCB。而FPGA有助于解决上述一些功耗约束难题。

便携式超声系统在小型封装中集成了众多不同类型的组件。每个组件都有不同的接口要求,这就需要我们采用多样化的连接解决方案。

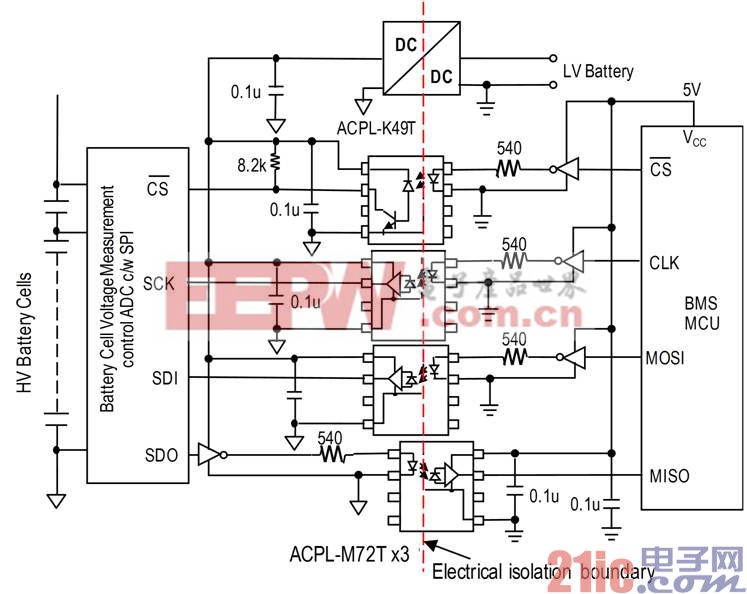

便携式超声系统接口存在三大问题。其一,就是波束形成器逻辑和数据转换器之间AFE接口的I/O数量较多。JESD204A为未来的超声系统提供了极富吸引力的解决方案。

其二,就是前端和后端处理模块之间的问题。为了尽可能减少I/O数量,我们通常在两个不同领域之间使用高速SerDes链接。在高端系统中(通常为购物车外形),我们可用PCIe背板来满足高带宽要求。图7给出了现代便携式超声系统中的主要接口。

图7 典型便携式超声接口

其三,就是设计人员往往受制于常用组件的成本和I/O方面的限制。FPGA能够让设计人员在单个器件中集成多种系统功能。该器件将一系列可配置存储器、DSP和I/O与大量逻辑单元紧密集成在一起,并采用先进的工艺技术制造而成。单个器件系统集成大幅降低了物理PCB级连接的技术挑战和成本压力。由于FPGA芯片由FPGA制造商设计,因此用户不必担心NRE及生产成本。用户只需创建设计,把设计文件下载到FPGA器件上,就能完成特定设计的配置工作。

赛灵思FPGA在便携式超声系统中的应用

赛灵思FPGA可帮助便携式超声供应商更好地推出小型化高性能低功耗产品。

降低功耗

降低功耗的主要原因在于:(1)在电池或发电机供电情况下延长工作时间;(2)减少对电源性能的需求(电源性能受制于严格的质量与安全控制要求);(3)最大限度地减少系统热量,从而减少散热管理设计的成本、尺寸和重量。

赛灵思FPGA能够在技术、架构和设计工具三个方面进一步降低便携式超声设计的功耗。

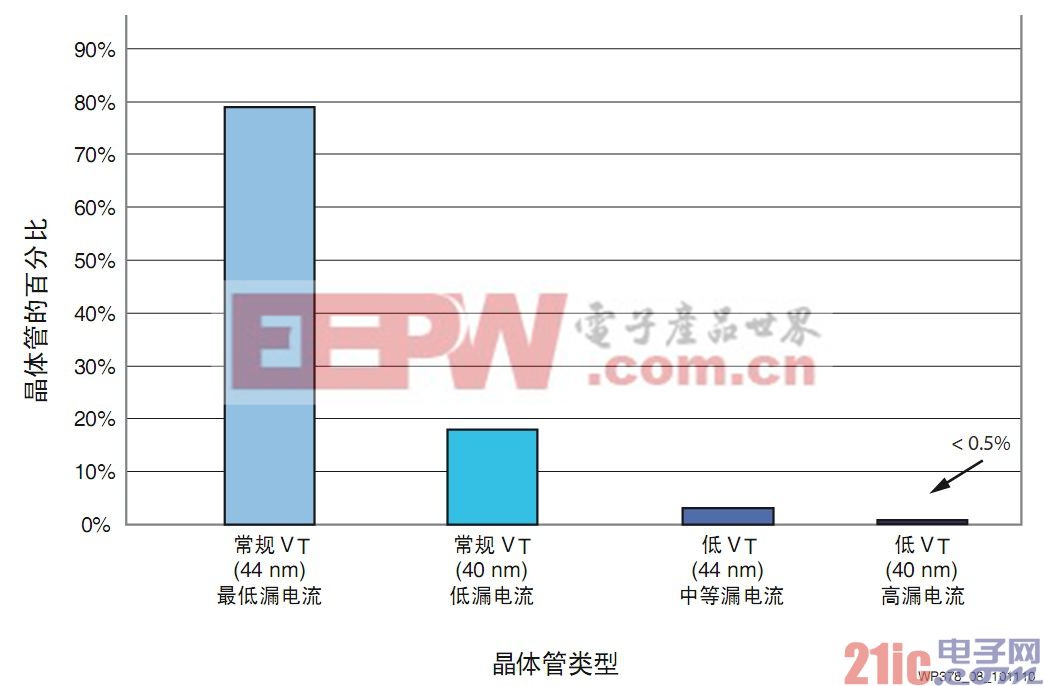

图8显示了Virtex-6器件的一般晶体管组合,能够以最低功耗满足所需的性能基准要求。这种方案也在7系列FPGA中得以延续,而且与前代产品系列和业界竞争型FPGA相比,利用28nm定制工艺能将静态功耗锐降40–80%。

图8 Virtex-6 FPGA中的8种晶体管类型分布

降低功耗不仅限于工艺技术层面,通过采用较低功耗的LUT6架构,实现更多时钟门控选项以及嵌入PCI Express、以太网MAC等关键IP模块,并创建更直接的路由选项,我们能够进一步降低功耗,从而减小连接点之间的电容。对于需要最小化功耗的应用领域而言,相对于前代FPGA而言功耗也能实现50%的显著改进。

fpga相关文章:fpga是什么

模数转换器相关文章:模数转换器工作原理

评论