全数字跟踪接收机的设计与实现

数字下变频部分设计的运算都集中在数字滤波部分,为减少运算首先对I、Q信号进行CIC抽取。CIC滤波器是一种基于零极点相抵消的FIR滤波器。本文设计是一个5级级联32倍抽取CIC滤波器,包括5级积分器,10倍抽取器和5级梳状滤波器。它们分别用累加器、序列变换和减法器用Verilog编程实现。

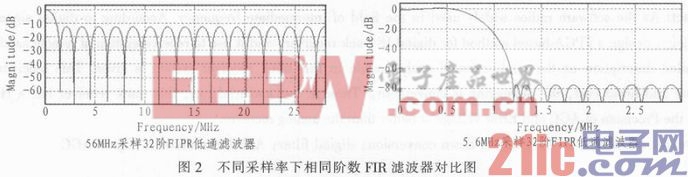

最后通过一个32阶的FIR低通滤波器:通带截止频率为0.6 MHz,阻带起始频率为1.2 MHz。用MATLAB的Smuilink的数字信号处理工具计算滤波器系数。比较抽取前后的滤波器以及资源占用情况。很明显抽取后的FIR低通滤波器要优于抽取前的,如果要在高采样率下达到抽取后的效果,就需要滤波器有个高的阶数,从而占用更多的资源。

2.3 包络检波

包络检波由开平方![]() 根和环路滤波器组成。经过抽取的信号经过开平方根后得到信号能量,再送到环路滤波器除去高频分量,得到信号包络信息。环路滤波是由一个2阶IIR低通滤波器和一个1阶IIR低通滤波器级联组成,构成一个三阶窄带滤波器,可以得到信号长期电平估计。这样可以保证增益因子不会因为接收信号的快速波动而发生较大变化。

根和环路滤波器组成。经过抽取的信号经过开平方根后得到信号能量,再送到环路滤波器除去高频分量,得到信号包络信息。环路滤波是由一个2阶IIR低通滤波器和一个1阶IIR低通滤波器级联组成,构成一个三阶窄带滤波器,可以得到信号长期电平估计。这样可以保证增益因子不会因为接收信号的快速波动而发生较大变化。

评论