基于FPGA和BU-65170的1553B远程终端设计与实现

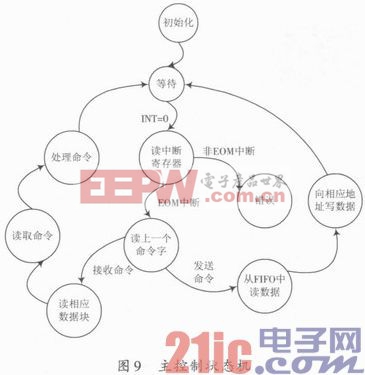

3.5 主控制器

FPGA中控制与BU-65170通信的主控制状态机如图9所示。初始化完成后程序进入等待状态。此时如果收到中断信号(INT=0),则首先读取中断寄存器,判断是否为消息结束中断(EOM),如果不是,进入错误状态,等待BC对RT进行检查或重启RT;如果是消息结束中断,则继续读取上一个命令字,若是发送命令,则从FIFO中读取28 B的状态信息数据,接着向相应的发送子地址数据块填写数据,在RT收到下一个发送命令后,BC从相应子地址读取上一条数据,这与对BU-65170进行读操作的原理相似。如果上一个命令字是接收命令,则读取相应子地址对应的数据块,然后读取具体命令内容,再根据命令进行相应的处理,最后回到等待状态。本文引用地址:http://www.eepw.com.cn/article/189492.htm

接收子地址1工作在双缓冲模式,用于接收BC发送的广播时间码,加载到每一条从RT发送到BC的状态信息的头部。双缓冲模式可以使FPGA访问指定子地址刚接收到的消息,RT将接收的数据字交替存储到数据块0和数据块1中。当FPGA需要访问接收子地址1内的消息时,首先将其改成单消息模式,读取数据块地址,并将其bit5的值取反得到“非活跃”数据块的地址,读取其上的最新时间码后再将接收子地址1改为双缓冲模式。

4 测试

选用Alta公司的ECD54-1553多功能板卡(能模拟BC\RT\BM)作为BC,与设计的RT搭成一个测试系统,如图10所示。

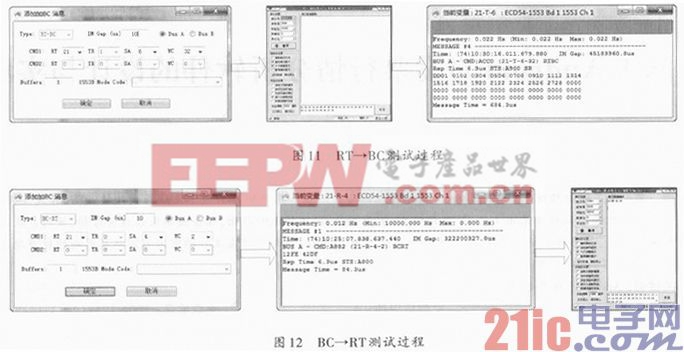

首先在ECD54-1553的控制界面中设置RT地址为21,然后根据在FPGA逻辑中设定的RT子地址及传输数据量进行相应的设置,再开启总线监控(BM)功能,测试RT→BC的过程如图11所示。设置RT地址为21、发送子地址为6、数据量为32个字(2 B标志位+28 B数据+2 B保留位);通过串口调试助手从PC机向RS 422发送28 B数据;经过FPGA处理后传送给1553B总线控制器,BM显示总线控制器正确收到从RS 422发来的数据。测试BC→RT的过程如图12所示。

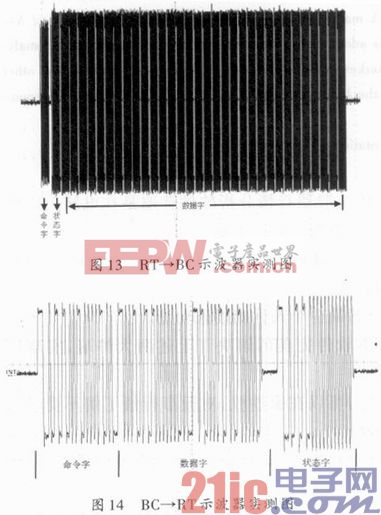

设置RT地址为21、接收子地址为4、数据量为2个字;由BC发送2个字的数据12FE 42DF;串口调试助手显示RS 422正确接收到BC发送过来的数据。示波器测得的实际曼彻斯特Ⅱ型码波形如图13,图14所示。

测试结果表明RT能正确、稳定地跟BC进行通信,达到工程项目所需的要求。

5 结语

本文设计了基于FPGA和BU-65170的1553B远程终端,实现1553B通信。详细介绍了硬件连接、BU-65170芯片配置、FPGA逻辑模块、UART设计、测试过程和结果。通过引入RS 422接口,更加直观地观测到1553B通信过程,易于调试。采用FPGA的最大优点是能迅速移植代码,缩减研发周期。随着技术的发展,对数据传输和处理提出了更高的要求,未来可以把控制其他子系统的模块和数据处理功能集成在一块FPGA芯片中提高集成性,便于开发和维护。

fpga相关文章:fpga是什么

评论