基于FPGA和BU-65170的1553B远程终端设计与实现

3.1 读/写模块

根据芯片手册给出的CPU读写时序图编写程序,在FPGA中实现对BU-65170寄存器和内部RAM进行读写的模块。读写模块的仿真时序图如图4和图5所示。本文引用地址:http://www.eepw.com.cn/article/189492.htm

在读写过程中,信号BU_RD_WR为‘1’时表示对BU-65170进行读操作,为‘0’时为写操作;信号BU_MEM_REG为‘1’时表示对内部RAM进行读/写,为‘0’时表示对寄存器进行读/写。在零等待模式中,信号BU_STRBD和BU_SELECT(可与BU_STRBD绑定,所以没有给出)控制着读/写操作的开始。

在长STRBD模式下SELECT和STRBD同时为低电平的第2个CLK上升沿,内部锁存MEM_REG和RD_WR信号;短STRBD模式下STRBD上升沿内部锁存MEM_REG和RD_WR信号。考虑到容易满足时序要求,采用长STRBD模式。当BU-65170锁存住MEM_REG或RD_WR信号后,BU_READY会出现一个上升沿,紧接着当BU_READY出现下降沿时,表示BU-65170内部传送周期已经结束。

在16位零等待模式下,写一个内部存储单元或寄存器时,只需执行一次写操作,使该字的地址和数据呈现在地址总线和数据总线上即可。而读一个内部存储单元或寄存器时,需要进行两次读操作。第一次读时,要读单元的地址和位置出现在A13-A00和MEM_REG上,这个周期独处的数据应忽略掉;第二次读时,相应的数据会出现在数据总线上。

因此,如果FPGA要执行一个多字读操作,地址总是早于对应的读出数据,在同一个周期上,地址总线上出现下一个字的地址,数据总线上出现前一个字的读出数据。

3.2 配置模块

BU-65170有17个寄存器,通过配置这些寄存器来选择工作模式和具体功能。选择增强模式、增强中断使能模式,使能RT子地址控制字中断,服务请求自动清除。初始化流程如图6所示,寄存器详细配置如表3所示,具体子地址设置如表4所示。

3.3 时钟模块

使用40 MHz的外部晶振作为FPGA的时钟输入,然后用FPGA自带DCM模块分频得到16 MHz主时钟,作为其余模块的全局时钟,仿真和实际波形测试表明全局时钟稳定性良好,满足系统要求。

3.4 RS 422控制及UART模块

RS 422模块实现了RS 422通信功能,一方面满足了工程要求;另一方面也使调试1553B系统变得方便明了,因为1553B发送过来的数据可以立即通过RS 422转RS 232接口显示在PC机上,同理,可以通过PC机发送数据到1553B的总线控制器。1553B总线接收数据的过程如下:RS 422端口发送数据到FPGA,将数据缓存在FIFO中,RT接收到发送命令后,FPGA把FIFO中的数据写入RT相应的发送子地址,最后再由RT发送给BC。类似地,1553B总线发送数据的过程如下:RT接收到接收命令后,FPGA立刻把数据从相应子地址读出,并传送给RS 422模块,再通过UART将数据发出。

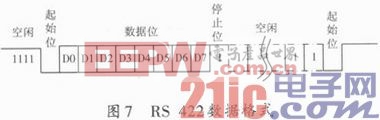

UART采用10位异步通信方式,即1个起始位,8个数据位,1个停止位,如图7所示,波特率为9 600 b/s。RS 422控制模块内部包含一个分频模块,将产生RS 422接口定义中的收发所需的波特率。通过对于系统时钟的分频,产生波特率为9 600 b/s和153 600的信号。

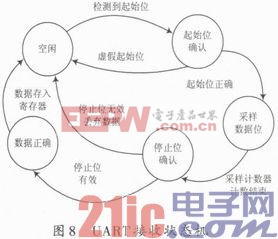

接收状态机见图8。当检测到起始位时,首先检验起始位是否正确,如果正确,立即采样数据位,否则就返回空闲状态。当采样计数器计到8后判断下一位是否为停止位,若不是,则丢弃数据并进入空闲状态;若是,则把数据存入寄存器后进入空闲状态,结束一次成功的接收。为了提高正确率,还采用三模冗余算法。UART发送过程与接收类似,在收到发送信号后将需要发送的数据存入缓存,在使能有效和缓存不空的情况下开始传输。此时指针开始计数,首先发送起始位‘0’,接着一次发送8 b数据,最后发送停止位‘1’,结束一次发送过程。

fpga相关文章:fpga是什么

评论