A/D转换器测试技术及发现ADC中丢失的代码

A/D转换器的量化噪声、丢失位、谐波失真以及其他非线性失真特性都可以通过分析转换器输出的频谱分量来判定。

本文引用地址:http://www.eepw.com.cn/article/189042.htm确定由上述这些非线性特性所引起的转换器性能的下降并不困难,因为这些都呈现为A/D转换器的输出噪声中的一些杂散频谱分量以及背景噪声的增加。传统的测量方法是将模拟的正弦电压加到A/D转换器的输入端,然后测量转换器的数字化时域输出采样的频谱。

可以利用FFT来计算A/D转换器输出采样的频谱,但是为了改善频谱测量的灵敏度,必须将FFT频谱泄漏减到最小。但对于高性能的A/D转换器测试,传统的时域开窗无法足够地降低FFT泄漏。

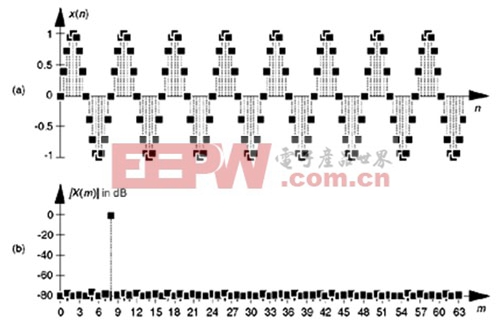

解决FFT泄漏的诀窍是采用频率是A/D转换器时钟频率整数倍的模拟正弦输入电压,如图1(a)所示。该频率为mfs/N,m是整数,fs是时钟频率(采样率),而N是FFT点数。当理想A/D转换器的模拟输入为N = 128转换器输出的8个周期采样正弦波时,图1(a)中x(n)是其时域输出。

图1:当输入为一个模拟的8fs/128 Hz正弦曲线时,理想A/D转换器的模拟输入为:(a) 输出时域采样;(b) 以dB为单位的幅值。

该例中,输入频率被归一化到采样率fs,即8fs/128 Hz。mfs/N定义了离散傅里叶变换(DFT)的分析频率,或频率段中心(bin center),频率位于频率段中心的DFT输入正弦曲线不会引起频谱泄漏。

在图1(b)中,用对数坐标绘制了x(n)的128点FFT的前半部分,输入频率刚好位于m=8的频率段中心,FFT泄漏得到了有效减小。特别地,如果采样率为1MHz,则A/D的模拟输入频率将必须精确为8(106/128) = 62.5 kHz。

为了实现这一方案,需要确保模拟测试信号源与A/D变换器的时钟频率fs Hz保持精确同步。这也正是为什么A/D转换器测试过程被称作为相干采样的原因。

也就是说,模拟信号发生器和提供fs的A/D时钟发生器在频率上不能有彼此的漂移,必须保持相干(从语义上必须注意,有时候正交采样也被称作为相干采样,不过正交采样与这里的A/D转换器测试过程无关)。

正如所预见的那样,m中的某些值比其他的一些有利。注意图1(a)中,当m=8时,A/D转换器只输出9个不同的幅度值。这些值不断地反复。如上图2中所示,当n=7时,就要比9个不同的A/D输出值多很多。

图2:7周期的正弦A/D转换器输出。

选m为一个奇素数

由于最好能够测试尽可能多的A/D输出二进制字,同时又要保持量化噪声足够随机,A/D测试方案的用户发现了另一个窍门。他们发现当m选为奇素数(3、5、7、11)时,能够将A/D输出字的重复减到最小。

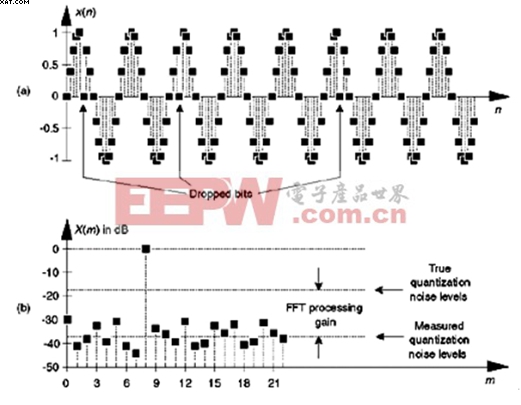

下面的图3(a)显示了一个非线性A/D转换器工作的一个极端例子,有几个离散输出将采样位下降到m=8的时域x(n)中。图3(b)提供了这种失真的x(n)的FFT,与图1(b)进行比较,可以看到噪声背景增加了,这是因为A/D转换器的非线性所致。

图3:非理想的A/D转换器输出表现出几个丢失位:(a)时间采样;(b)频谱幅值(单位dB)。

评论