采用FPGA的振动模拟器设计

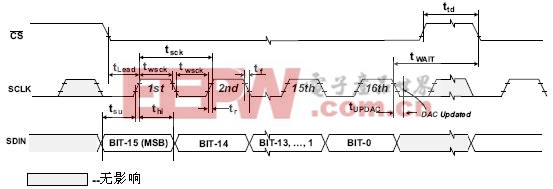

图3 DAC8581 时序图

图4 DAC8581时序要求

4.1 FPGA对ADS1100芯片的控制

调频和调幅信号使用同一款芯片:ADS1100,16位串行,I2C接口,在本设计中数据更新率是8SPS,电压型输出。此芯片仅可在从件模式下工作。ADS1100将模数转换结果传给FPGA模块,由FPGA进行串并转换。

FPGA对ADS1100提供SCLK和SDA引脚,符合I2C协议。FPGA是主器件,在开始与ADS1100通信前先对SDA写2个字节,分别确定和哪个ADS1100进行通信和对ADS1100的配置寄存器(configuration register)进行写以确定对其的操作模式。FPGA外接24MHz的晶振,经分频得到4MHz的时钟,ADS1100按8SPS的数据更新率工作,FPGA探测数据线变化以产生SCLK时钟信号赋给SCLK引脚。篇幅受限,I2C的FPGA实现不一一赘述。

4.2 FPGA对DAC8581芯片的控制

信号输出使用芯片DAC8581,16位串行,SPI接口,在本设计中最高数据更新率是1.8MHz,电压输出。DAC8581接收从FPGA传送过来的串行数据,将其进行数模转换,产生振动信号,模拟实际振动台的理想振动情况。

FPGA中,由PLL倍频得到36MHz的时钟提供给DAC8581的SCLK引脚。由调频信号计算得到串行DAC的数据更新率,按此频率更新串行DAC的数字输入。由同一个PLL倍频得到240MHz的时钟捕捉将由DAC处理的数字输入信号和SCLK引脚信号的跳变沿,从而产生DAC8581的CS片选信号。

数据data一旦准备好,赋给register,240MHz时钟探测到第一次SCLK上升沿,就拉低CS片选,第二次探测到SCLK上升沿时已经至少是下一个240MHz的上升沿了,从而满足Tlead(见图3、图4)参数的要求。CS低时,一旦240MHz时钟探测到SCLK下降沿,将register的最高位数据赋给SDA,将register左移一位,SDA保持不变,直到下一个SCLK下降沿。当捕捉到SCLK的第17个下降沿时,将CS拉高。由此即可满足以上的图3、图4对时序的要求。

4.3 FPGA对DAC8820芯片的控制

DAC8820产生振动噪声。16位并行,最高数据更新率4MHz,是电流输出型。本系统设有2个用户按键,分别表示产生40KHz~100KHz,100KHz~200KHz的噪声频率范围,FPGA接收按键信号确定噪声的频率范围,在此频率范围内产生一个随机频率,由此计算得到DAC8820的数据更新率,FPGA按此频率准备数据以更新并行DAC的数字输入。由DAC8820将其进行数模转换,模拟实际振动台在可能受到外界各种干扰信号后产生的噪声情况。

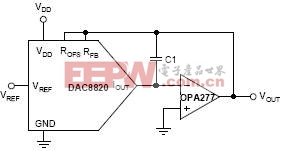

图5 DAC8820外部电流电压转换电路

DAC8820的引脚WR(低有效)是将16位数据加载到输入寄存器;LDAC(高有效)是将数据从输入寄存器加载到DAC寄存器;但是若将同一信号同时赋给WR和LDAC,则可在下降沿将16位数据加载到输入寄存器,在上升沿将数据从输入寄存器加载到DAC输出。

由FPGA将24MHz的晶振时钟分频得到数据更新率,由此得到的时钟信号经高频时钟同步赋给DAC8820的WR和LDAC。由于DAC8820是电流输出的,所以将电流输出经过OPA277电流电压转换输出,见图5。图中的C1是补偿电容,其作用是防止增益峰值的出现。

5 结论

综上,此振动模拟器的调频信号的分辨率是16比特,可产生0 ~5kHz的清晰信号,所以频率精度可达到0.076Hz,并可与200KHz以下的确定频率范围的随机噪声进行合成,输出信号幅度分辨率可达16比特,而且噪声的频率范围是可控的。

本文作者创新点:充分利用了FPGA可现场编程的特点,给读者提供了一个实施简单,成本低,可按用户需求灵活改变,且易升级的振动模拟器的设计方案;且对有特殊要求的信号发生器的设计有一定借鉴意义。

评论