DC~40 GHz反射型GaAs MMIC SPST开关

随着GaAs MMIC技术的发展和成熟,人们对高性能、小型化、超宽带开关的要求越来越迫切。GaAs MMIC开关具有开关速度快、插损小、可靠性高、驱动功耗几乎为零、体积小等特点,能够满足工程应用的系列要求。SPST开关作为电子系统中射频信号调制、信号通断的元件,现今在实际工程中已经得到广泛的应用。

本文系统地介绍了一种单片SPST开关电路研制过程。SPST开关电路结构采用具有宽频带的三并FET器件结构。这种结构具有低插入损耗和宽频带等优点。同时,对比不同的通孔数量,分析了通孔电感对电路性能的影响。

1 宽带单片SPST开关的设计

1.1 开关FET器件的工作原理

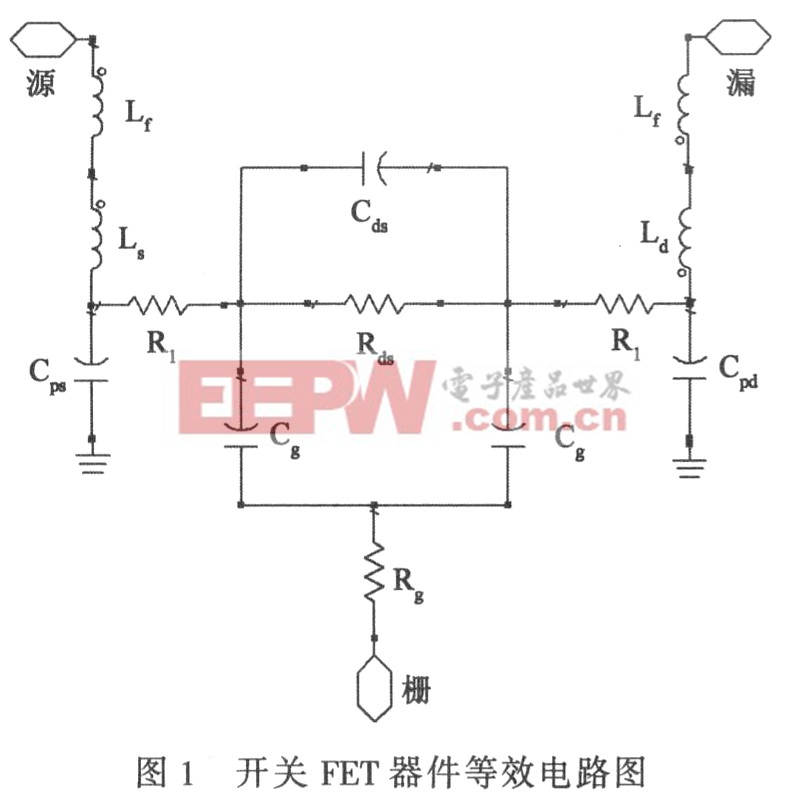

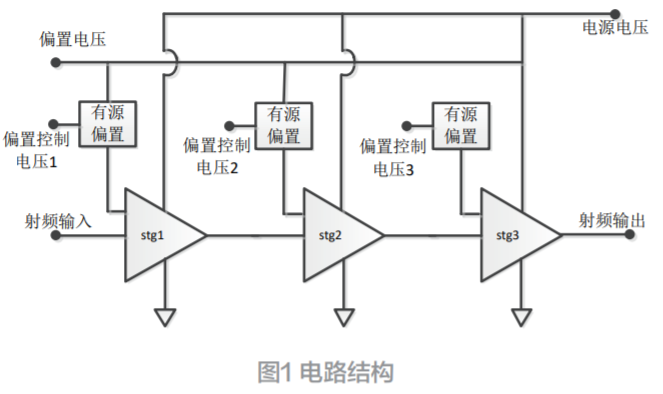

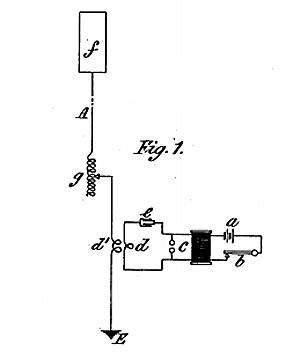

开关设计过程中,主要使用的元器件是开关FET器件、微带拐角和微带传输线等。开关FET器件是核心元件,器件的衬底材料、物理参数和工艺制作直接影响开关FET的微波性能。FET开关器件是一种三端口压控电阻,栅偏置电压Vg控制开关的状态,控制沟道中源漏电阻的大小。分析文献得出,本征栅源电容和漏栅电容、器件的寄生参数限制FET开关的高频性能。开关FET器件等效电路如图1所示。

图中的Cps、Cpd、Ls、Ld和Lf为器件寄生电容和电感,Rg为栅隔离电阻。Rds和Cg在开态和关态有不同的值。所有元件都表征为器件栅宽和栅指数的函数。理想情况下,Rds和器件总栅宽成反比例关系,Cg和器件总栅宽成正比例关系。

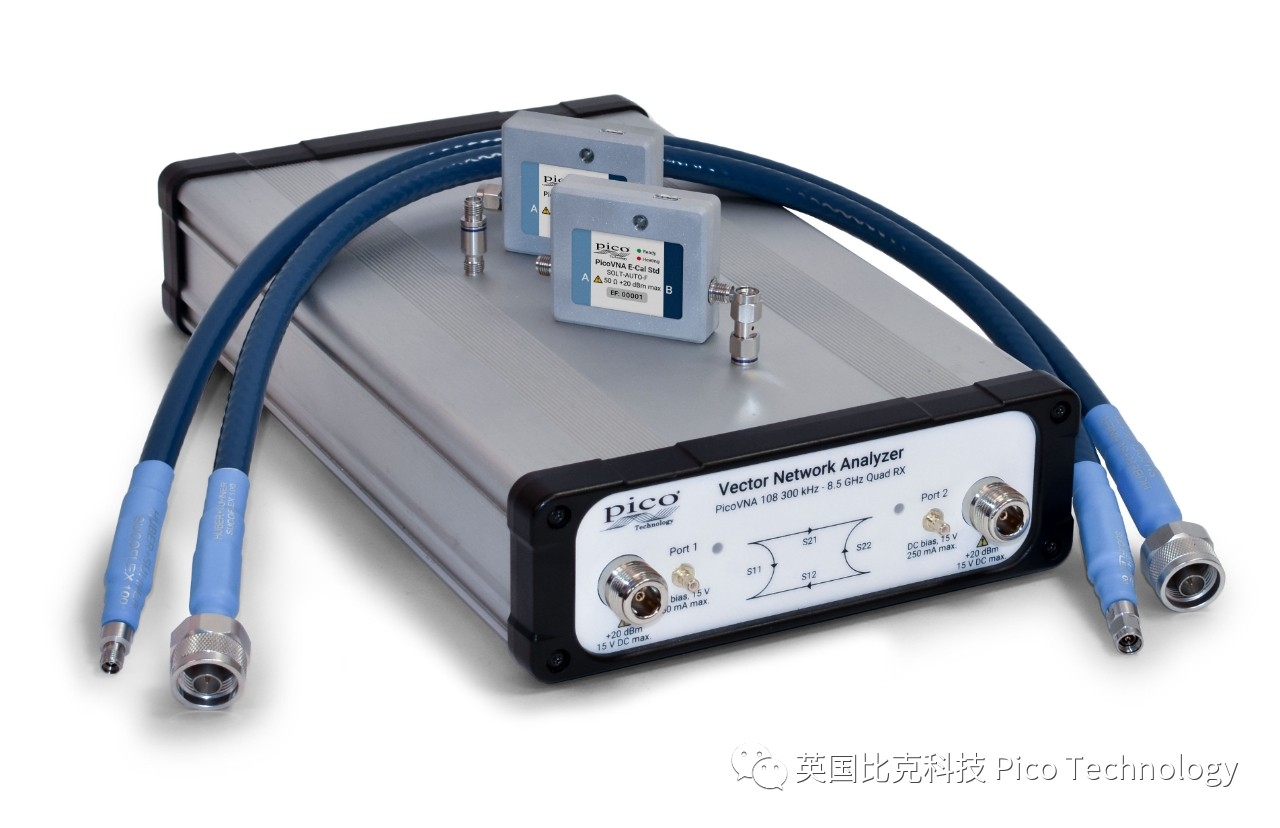

1. 2 开关FET器件在片测试及建模

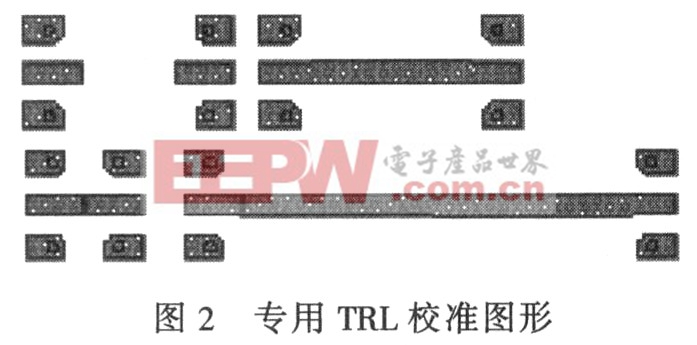

在整个研制过程中,开关FET器件模型是电路设计工作的保障,而且是一个持续的、不断修正的过程。本开关单片使用的开关器件模型是基于器件的在片测试结果所提取的小信号模型。首先针对建模器件测试图形设计专用TRL(直通\反射\传输线)在片校准图形,采用该校准图形对矢量网络分析仪E8363B进行在片校准,测量器件不同栅压情况下的小信号S参数。然后,用建模软件对开关FET器件等效电路模型所需的参数进行统计分析,拟合测试所得到的小信号S参数,得到模型的参数值。

同时,在前期研制工作中,对TRL(thru,reflect,line)校准方式进行了相关的理论分析。TRL校准是准确度比SOLT校准更高的一种校准方式。通常来说,TRL标准件的要求如下:

(1)直通标准件:电气长度不为O时,直通标准件的特性阻抗必须和延迟线标准件相同,无须知道损耗,当群延时设为0 ps时,参考测量面位于直通标准件的中间;(2)反射标准件:反射系数的相位必须在正负90°以内,反射系数最好接近1,所有端口上的反射系数必须相同;(3)传输线标准件:传输线的特性阻抗作为测量时的参考阻抗,系统阻抗定义为和延迟线特性阻抗一致。延迟线和直通之间的插入相位差值必须在20°~160°,如果相位差值接近0°或者180°时,由于正切函数的特性,很容易造成相位模糊。

开路标准件实现起来最容易,但是由于开路标准件存在边缘电容效应,所以还通过3D-EM仿真来获得开路标准件的边缘电容。本电路建模时,专用TRL校准图形如图2所示。

本宽带低插损开关电路对开关FET器件模型的提取提出更高的要求,模型的频率响应要求更高。实测模型小信号S参数的数据准确度,直接影响模型的精度。本文还对引起测量误差的几种情况进行了分析。通常,网络分析仪的误差可以分为漂移误差、随机误差和系统误差三类。漂移误差主要是由温度变化造成的,可通过重新校准来消除;随机误差主要是由仪器的噪声、开关的重复性和射频电缆接头的重复性引起的。降低随机误差的最好方法是减小中频带宽或多次扫描下进行示迹平均,但测量的时间将受到影响;系统误差是测量不确定度的重要来源。

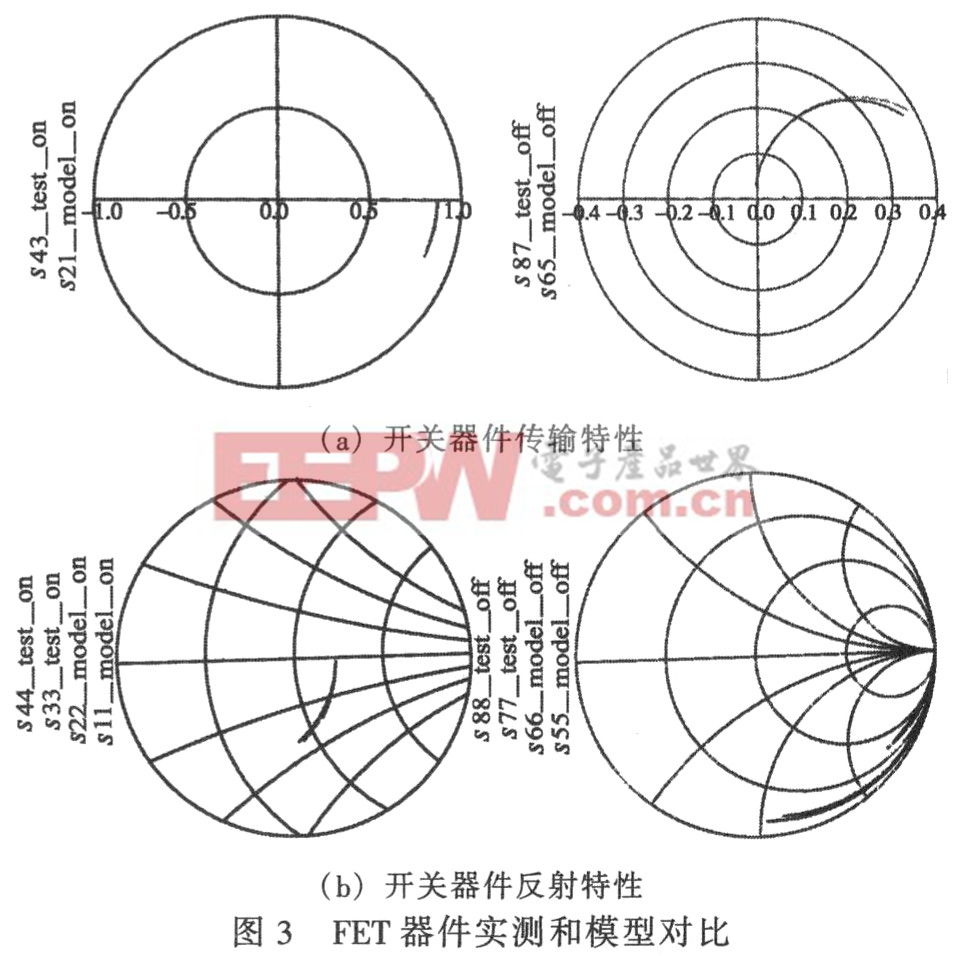

图3是2×50μm FET器件传输特性和反射特性的实测和模型对比情况。从图中可以看出在DC~40 GHz的频率内,模型参数取得非常满意的拟合结果。

1.3 SPST电路的设计

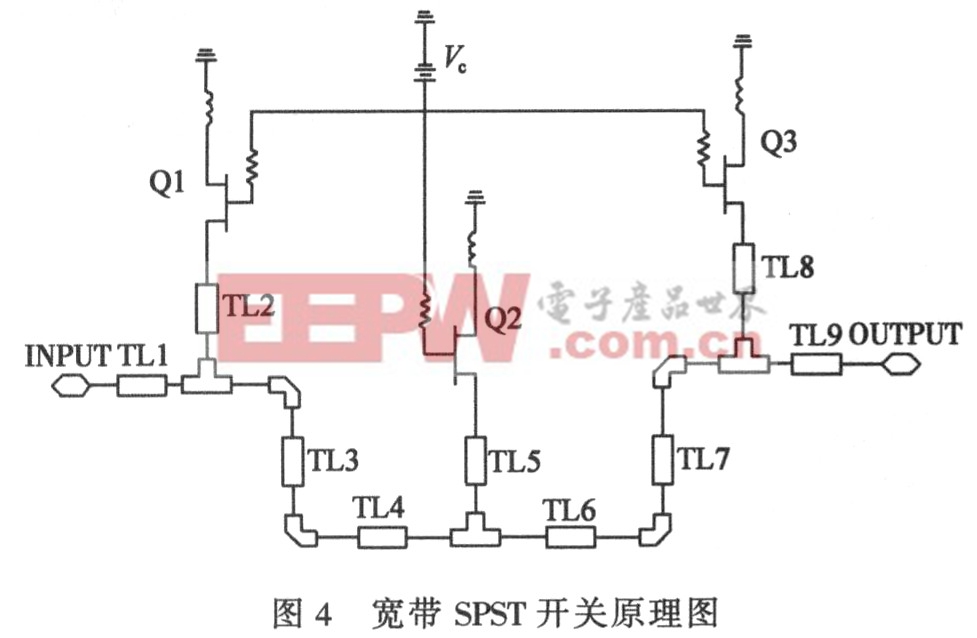

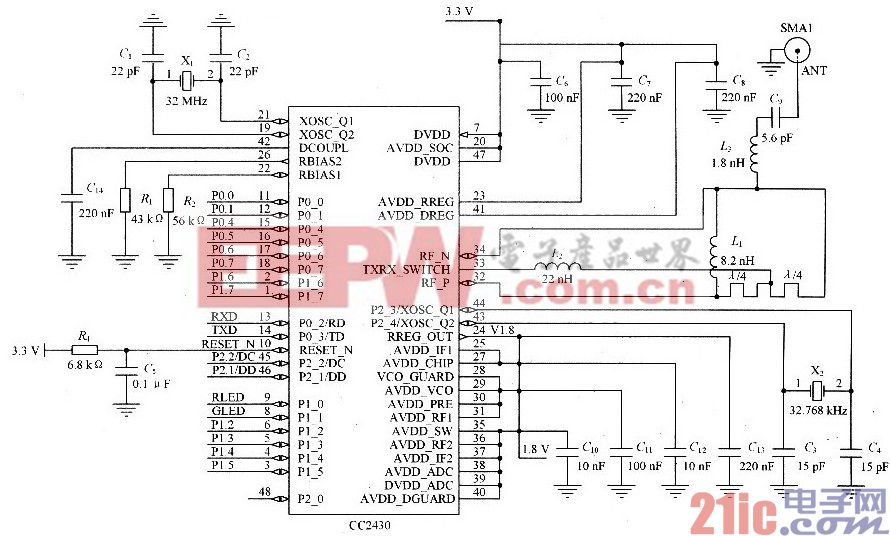

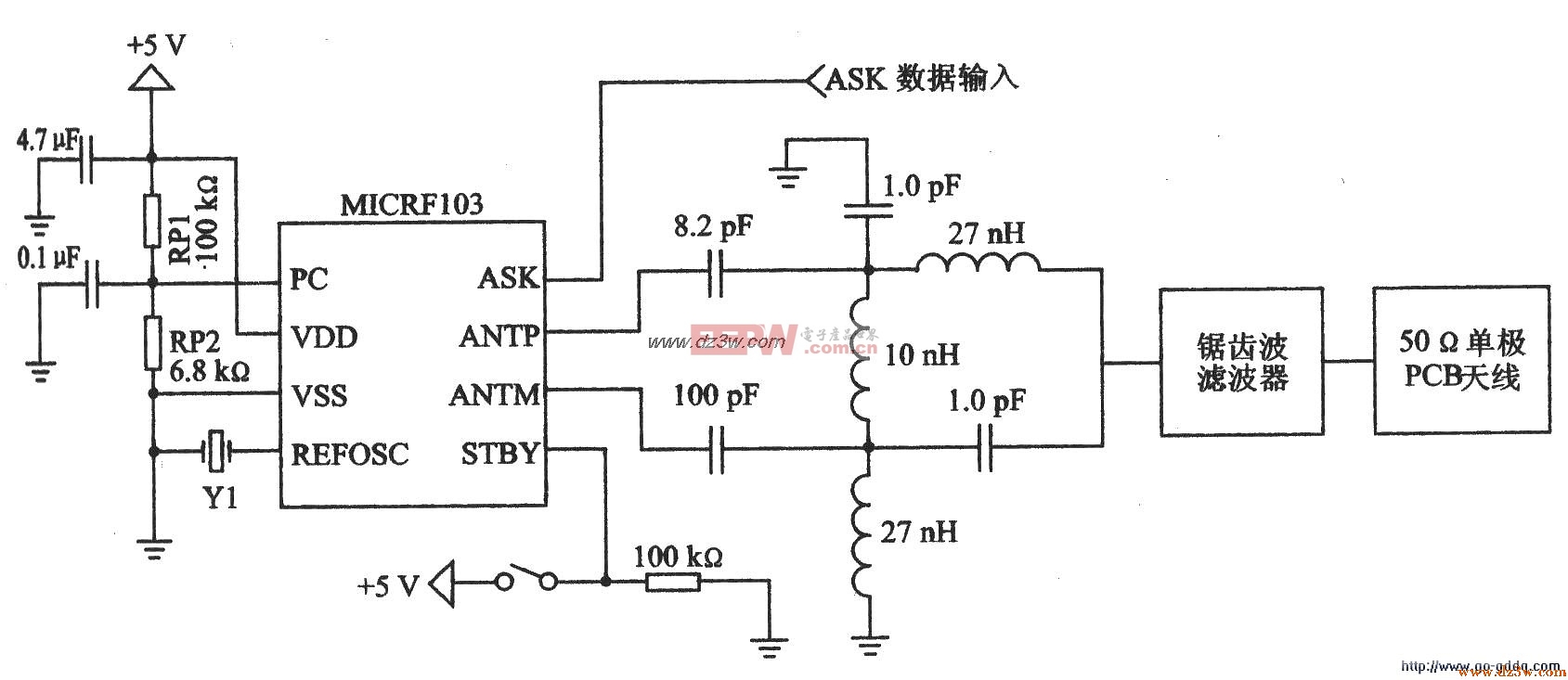

在电路设计过程中,采用分布参数的原理图和电磁场仿真相结合的方法,开展了电路设计。SPST的电原理图如图4所示。电路拓扑结构采用三并联器件结构,该种结构只需一个控制端来实现开关的导通和关断。

在分布参数的原理图设计过程中,当取得满意的设计结果,将设计参数在版图中实现,进行电磁场分析,充分考虑无源电路部分的色散、辐射和耦合等影响,进而弥补电原理图设计精度的不足。图5是宽带SPST电磁场分析时网格的部分情况。

评论