3.7 GHz宽带CMOS LC VCO的设计

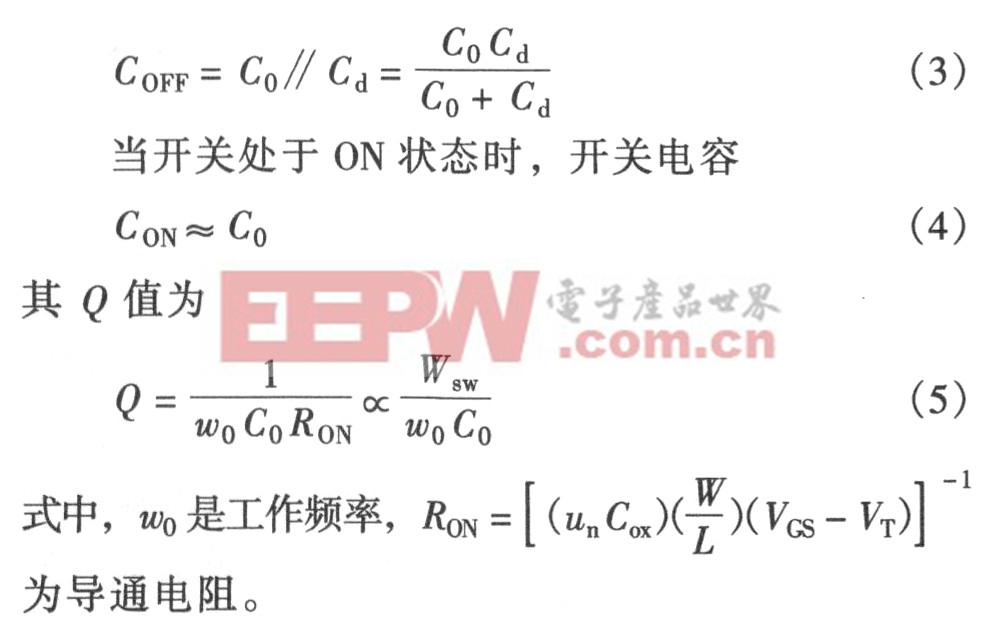

当开关处于OFF状态时,开关电容本文引用地址:http://www.eepw.com.cn/article/188965.htm

振荡频率正比于![]() 因此调节范围取决于最大电容和最小电容的比值,由式(3)、(4)可以得到最大电容和最小电容的比值为

因此调节范围取决于最大电容和最小电容的比值,由式(3)、(4)可以得到最大电容和最小电容的比值为

![]()

从公式(5)、(6)可以看到开关电容最大的Q值与最大的调节比率之间存在冲突。C0由工作频率w0决定,因此Wsw在优化中是最重要的设计参数。

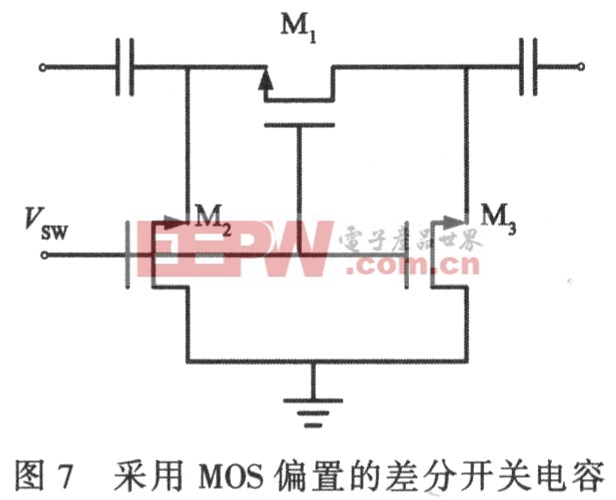

开关电容的Q值可以通过差分电容开关的方式来改善,如图7所示。当开关处于ON状态的时候只有沟道电阻RON的一半与电容串联,相比于单端的结构,Q值可以提高一倍。M2和M3为工作在亚阈值区的有源电阻,可以为MOS开关的源端和漏端提供直流偏置。

当Vsw设为0的时候,VD/S=0,VG=VDD,因此MOS开关管的VGs―VT达到最大,从差分端口看进来,等效电容达到最大,因此电路振荡在较低的频率上;当Vsw设为VDD时,VD/S=VDD,VG=0 V,电路工作在较高的频率上。

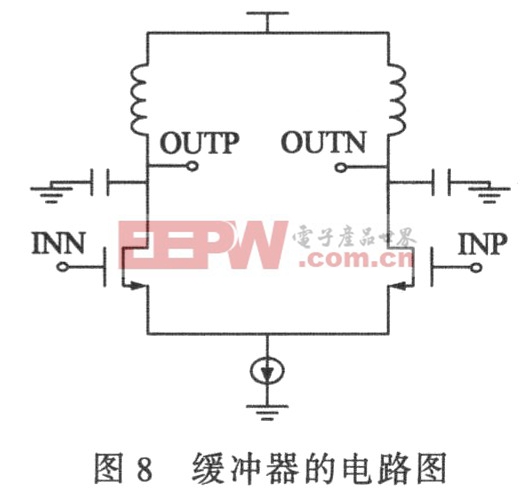

1.4 输出缓冲器及匹配电路的设计

为了将VCO的输出信号送到片外,考虑到外部电容很大,采用了电感负载的缓冲器,通过选择合适的电感和电容使其谐振在3.7 GHz,如图8所示。

在匹配电路的设计上,选用了π型匹配电路,首先利用spectreRF仿真得到输出缓冲器的S22参数,然后构建匹配电路使其阻抗达到50 Ω。具体的匹配电路(1.3 nH为邦线电感,94.9 pF的电容为隔直电容)及其Smith圆图如图9所示。

2 测试结果

本LCVCO是用于3.7 GHz锁相环的,整个锁相环是在和舰0.18μm混合信号工艺下制造的,整个VCO的面积为0.4 mm×1 mm,芯片照片如图10所示。测试得到的VCO的工作频率为3.4~4 GHz,有16%的调节范围,调节电容阵列开关得到的频率随控制电压的变化曲线如图11所示。在1.8 V电源电压下的功耗为10 mW;在1 MHz频偏处的相位噪声为一100 dBc/Hz。测试得到的VCO输出频谱如图12所示,输出功率相对较低,主要是由于对邦线的寄生电感和寄生电容估计出现偏差导致匹配电路没有实现完全匹配,但这对VCO性能的测试没有实质的影响。

3 结论

基于和舰0.18μmCMOS混合信号工艺设计了一款工作在3.7 GHz的LCVCO。本文着重论述了电感与射频开关的设计,通过采用电容开关阵列的方式增加了VCO的工作范围以补偿PVT的变化所带来的影响。测试结果表明,该VCO可用于锁相环和频率合成器。

评论