等离子显示器降功耗技术

● AwD方法――即“寻址的同时显示”。寻址、维持、擦除脉冲组合在一起施加,可降低寻址电压,从而降低无用功耗。同时,由于维持时间占据了一个子场的大部分时间,故维持脉冲的频率可以降低。

● 擦除寻址方法――即初始化后即进入维持发光阶段,待灰度等级到达要求后,通过擦除寻址使这些单元熄灭。因此,每场中单个像素的寻址只有一次。而且,可以用较低的擦除电压和电流,有效地降低寻址功耗。

● 改变脉冲电路的工作方式――即使开关元件尽量工作在开关管电压或电流接近零时开通或关断(ZVS或ZCS)状态,可降低器件本身的开关损耗。

在大尺寸的PDP显示屏中,行、列驱动IC的耗用量很多。其功耗大致分为三部分:逻辑部分、电平移位寄存器和高压驱动部分。正常情况下,逻辑部分功耗在20mW以下,电平移位寄存器部分在200mW以下,因屏电容部分的充放电而产生的高压驱动电路的无效功耗主要来自于回路中的寄生负载――电阻分量的损耗。这种电阻分量的存在是不可避免的,但对于电容充放电的电能,驱动IC可以通过内置能量回收电路的方式设法回收一部分。

为了满足高压器件工作性能的需求,降低高压驱动部分的无用功耗,PDP驱动IC在设计和工艺上需采取如下比普通的集成电路更为严格的控制措施。

● 采用SOI工艺结构,与常规功率模块相比能量损耗可大大降低

● 采用介质隔离,使驱动IC内部的输出嵌位二极管可避免串扰现象

● 对于内部元器件结构和布局等给予特殊地处理,利用内部控制可消除高压开关时的穿透电流

3 MOS管的选型

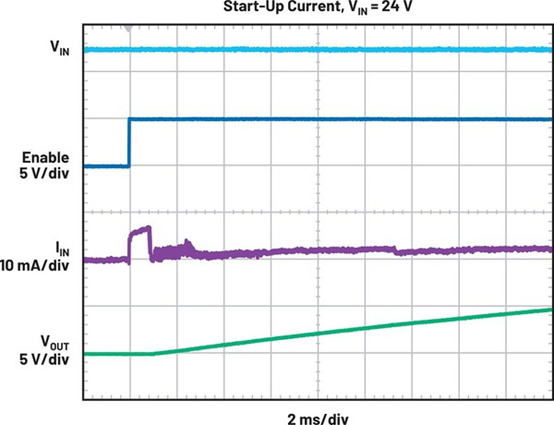

选择参数合适的功率场效应晶体管(MOSFET)可使驱动电路能够高效率、稳定地工作,且寿命满足要求。要求MOSFET的过渡要足够快,以便减少开关损耗;导通电阻足够小,以便减少导通损耗;关断电阻足够大,以便提高隔离作用。

其中,漏源导通电阻Rds(on)、反向恢复时间trr、输入电容Ciss和栅极总电荷Qg需认真考虑。低的导通电阻有助于减少导通损耗,特别是与“能量回收电路”相关的MOS管,低的导通电阻有助于提高能量回收的效率,降低PDP的功耗。trr、Ciss、Qg影响MOSFET的开关速度,低的参数值能够加快MOSFET的转换过程,有助于减少MOSFET的开关损耗。另外,低的Ciss和Qg参数,能够减少MOSFET栅极的驱动功率,简化栅极驱动电路的设计。

栅极驱动电路是影响MOS管开关损耗的外界因素,优良的栅极驱动电路与高性能的MOSFET相结合,才能制作出高性能的PDP驱动电路。

4 荧光粉材料

PDP用荧光粉和荧光灯用荧光粉非常相似,PDP主要使用的荧光粉有Y2O3∶Eu红粉、(Gd,Y)BO3∶Eu红粉、Zn2SiO4∶Mn和BaAl12O19∶Mn绿粉以及BaMgAl14O23∶Eu和MgBaAl10O17∶Eu蓝粉。(Gd,Y)BO3∶Eu粉和BaAl12O19∶Mn粉的衰减时间偏长,Zn2SiO4∶Mn的衰减时间对实际应用而言就更长了,因此需研究开发新的发光材料。荧光粉材料直接影响着PDP电视的发光效率和整机寿命。通常等离子电视的寿命指标是指亮度降到一半时的时间。目前新一代长寿命、高亮度的PDP专用荧光粉已经实现商品化。

5 电极结构

通过增加电极间隙来提高PDP的亮度和发光效率是一项非常有效的措施,但电极间隙增大,所需的工作电压会随之提高。为解决这一问题,可在维持和扫描电极(X电极和Y电极)中间增加一个浮动电极F。浮动电极在单元工作期间不加电压信号,但在单个维持电压脉冲期间,其上会产生一定的感应电势。由于F电极与其两侧的X、Y电极的间距很小,因而在这两个间隙处容易首先产生放电。在它们的导引作用下,引起X、Y之间的长间隙放电,从而可降低PDP所需的维持电压。

6 其他

包括逻辑控制部分、主芯板等,都需要充分考虑降低无用功耗的问题,例如,可以在逻辑控制部分采用门控时钟的方式,待机状态下关闭一切内部寄存器的动作,以此达到消除无用功耗的目的。

综合以上分析,可以看到,降低PDP功耗可以从多个角度考虑,正确的做法是多管齐下,齐头并进,从电源、驱动方式、荧光粉材料、放电室结构和新型高压工艺等多方面着手,以求达到最大程度的效率提高。

评论