基于电流折叠技术的CMOS全差分VCO设计

3 系统仿真

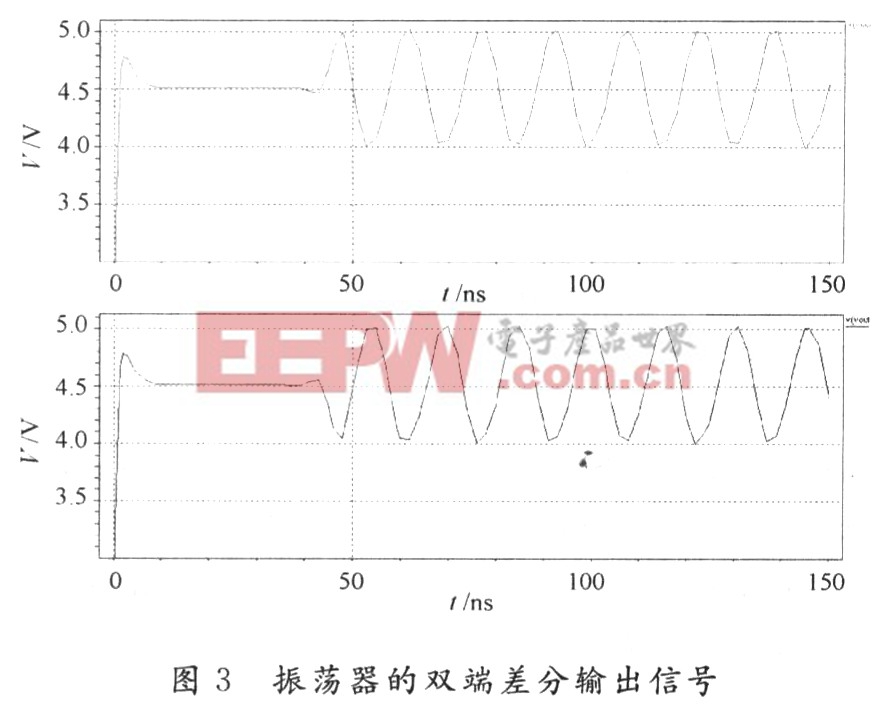

对整个系统在TANNER环境下利用Tspice工具和0.5/μm CMOS工艺库进行仿真。图3是2.5 V幅度控制电压和1.O V差动电压下差分振荡输出信号。仿真结果表明,起振时间仅52 ns,输出信号摆幅1.0 V,振荡频率66.25 MHz,功耗仅10 mW。

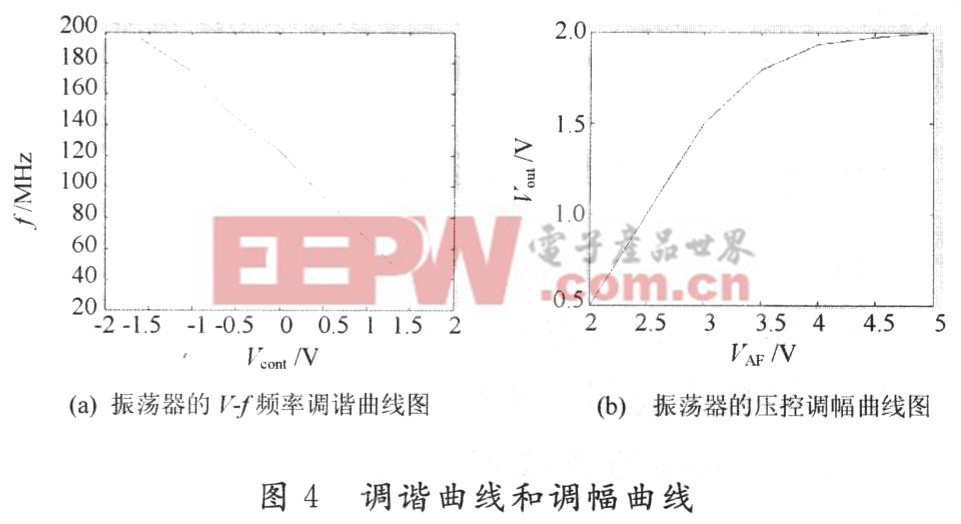

通常环振频率调谐范围在3倍以内,仿真表明振荡器在差分控制电压-1.6~+1.6 V范围内和2.5 V幅度控制电压下具有163 MHz约6倍(34~197 MHz)的宽调谐范围,并具有1.O V的常数振荡幅度,幅度偏差小于50 mV,如图4(a)所示。保持差分调频控制电压、调幅控制电压和振荡信号的幅度具有图4(b)所示的压控调幅曲线。表明在2.0~4.O V调幅控制电压下,具有较好的线性调幅特性,可在0.5~2.O V之间线性调幅。

4 结 语

设计的基于电流折叠的全差分压控调频调幅振荡器在O.5μm CMOS工艺下的Spice仿真结果表明,振荡器具有较大的频率调谐范围和调幅范围;压控频率调谐增益和压控调幅增益的线性度都较好;电路功耗较低,仅 10 mW;不需要电感和电容元件,便于CMOS工艺下的片上集成,并极大地减小了芯片面积。

基尔霍夫电流相关文章:基尔霍夫电流定律

电流传感器相关文章:电流传感器原理

评论