基于CPLD技术的PC104总线多功能扩展卡设计

多功能扩展卡的CPLD内部硬件设计包括:地址分配及译码电路、A/D模块控制电路、

D/A模块控制电路、开关量输入/输出模块控制电路和正交解码模块控制电路。

2.2.1 地址分配及译码电路

地址分配及译码电路包括基地址发生电路和地址译码电路。在与嵌入式主板组成系统时,相对于嵌入式主板而言,多功能扩展卡是一个外围设备,因此,首先要为该卡设置一个与系统内的其他外围设备不相冲突的基地址,这由扩展卡的基地址设置开关及CPLD内部地址分配及译码电路完成。地址分配及译码电路由数值比较器74688、译码器74154等构成,

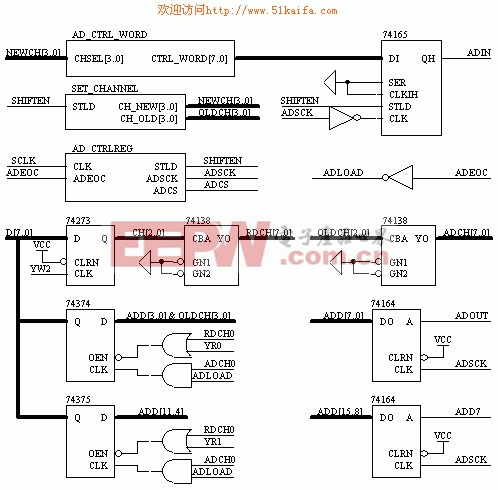

2.2.2 A/D模块控制电路

A/D模块控制电路的控制逻辑由两部分组成:其一是实现嵌入式主板通过总线访问各模拟通道的A/D转换结果,由模拟通道选择寄存器(74273)、转换数据寄存器(74374)等构成;其二是提供A/D芯片的接口时序,实现A/D芯片八个通道的自动采样和转换,由串/并数据转换逻辑(74164)、并/串数据转换逻辑(74165)、通道扫描控制逻辑(AD_CTRL_WORD)、A/D控制时序逻辑(AD_CTRLREG)等构成。A/D模块控制电路的电路设计如图3所示(转换数据寄存器只介绍一路)。本文引用地址:http://www.eepw.com.cn/article/188817.htm

图3 多功能扩展卡A/D模块控制电路

2.2.3 D/A模块控制电路

D/A模块控制电路由74373 IP软核及相应控制逻辑构成,功能是同时刷新D/A芯片的输入值。D/A控制模块电路采用两级锁存电路刷新D/A芯片的输入值,先置高4位字节数据,再置低8位字节数据,置低字节数据的同时使能D/A芯片的片选信号(/CS)、写信号(/WE),然后置数据锁存信号(/LDAC),刷新D/A的输出。

2.2.4开关量输入/输出模块控制电路

开关量输入模块控制电路由两片74244 IP软核及相应地址信号构成,开关量输出模块控制电路由两片74273 IP软核及相应地址信号构成。功能是实现嵌入式主板通过总线直接访问各路开关量。

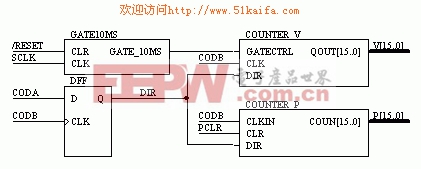

2.2.5 正交解码模块控制电路

正交解码模块控制电路是针对正交光电编码器设计的,由方向识别逻辑(DFF)、闸门时间定时器(GATE10MS)、异步清零位置可逆计数器(COUNTER_P)、异步清零速度可逆计数器(COUNTER_V)等构成,可用于测量电机输出轴的转动方向、位置、速度等运动信息。电路设计如图4所示。

图4 多功能扩展卡正交解码模块控制电路

3 结论

该多功能扩展卡已经成功地应用到国家体育总局奥运科技攻关项目“帆板摇帆训练测试系统研究”中,成功地完成了对交流伺服电机式阻力源的控制。访问协议与台湾研华PC工控机ISA总线板卡兼容,可获得组态软件编程支持。采用了复杂可编程逻辑器件(CPLD)技术,大大提高了系统的可靠性、灵活性。

伺服电机相关文章:伺服电机工作原理

评论