四通道可编程数字下变频器HSP50216及其在软件无线

HSP50216支持定点和浮点并行输入模式,其输出结果可在4-bit定点到32-bit浮点中选取,并可处理器接口进行编程。另外,所有被同步通道输出数据可都通过微处理器接口来读取。

VCC:3.3V电源电压端;

GND:电源地;

A(15:0),B(15:0),C(15:0):分别为并行数据输入总线A、B和C。当EAIN为低时,在时钟的上升沿采样。

D15~D0:并行数据输入端。从D15~D0,每连续四个端口一组共四组可分别作为调谐器通道A、B、C、D的载偿输入COF、载频补偿同步输入COFSync、重采样频率补偿输入SOF和其同步输入SOFSync端;

ENIA~ENID:分别为并行数据输入总线A、B、C、D的输入使能端,低电平有效;

CLK:输入时钟;

SYNCI/CO:分别为同步输入/输出信号;

RESET:复位端;

SD1A~D:分别为串行数据输出1的A~D;

SD2A~D:分别为串行数据输出2的A~D;

SCLK:串行输出时钟;

SYCNA~D:分别为串行数据输出1的A~D同步信号;

P(15:0):微处理器接口数据总线;

ADD(2:0):微处理器接口地址总线;

WR或DSTRB:微处理器接口写或数据选通信号;

RD或RD/WR:微处理器接口读信号;

ΜPMODE:微处理器接口模式控制;

CE:微处理器接口片选;

INTRPT:微处理器中断信号。

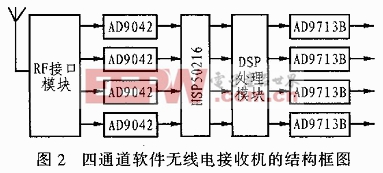

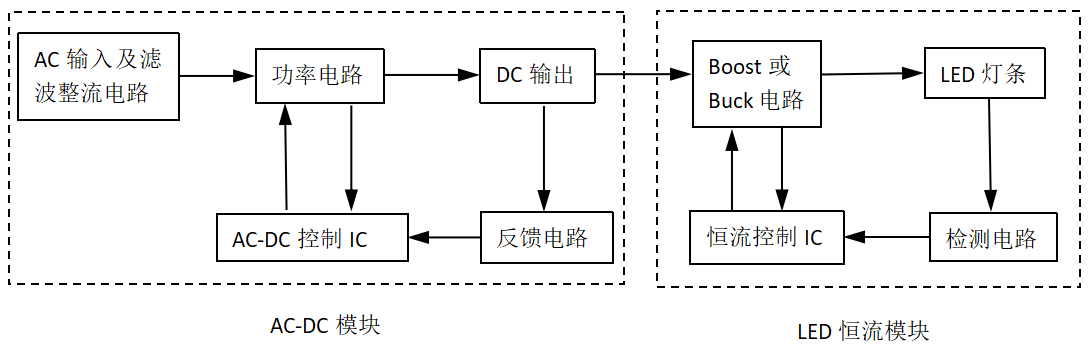

HSP50216 的最大特点是通过灵活的编程获得多样性的功能,可用于各种用途的电子信息接收系统,特别是用于多通道的软件无线电接收机。图2给出了一个实用的四通道软件无线电接收机的应用系统框图。该软件无线电接收机的硬件结构分为两部分,即从射频到中频的模拟部分和AD之后的数字部分。当电台在接收时,射频信号首先经过前端的接收和混频器后被转换到固定的中频,其中本地的载波频率相位以及有关的滤波器特性可由DSP来设定调整,以便适用不同的通信系统。每个通道的模拟中频信号通过A/D转换器AD9042后变为数字信号,然后再把每个通道的数字的数字信号送给HSP50216以将数字信号的载波频率进一步降低,并对输入信号进行抽取,因为这样可在允许的限度内减少信号数据的数量,便于被后面的DSP处理模块进行处理。由于运算量较大,可选用两片或更多浮点数据信号处理器TMS320C40进行各种处理,如信号检测、数字滤波、放大、解调和协议控制等。解调后的数字信号经D/A转换器AD9712B转换成模拟信号,这样即可完成电台的接收功能。

评论