高速串行数据收发器CY7B923/933及应用

MODE=H,收发送器工作于直传模式,即收发送器直接传输数据不编码,编码和解码由外部协议控制器完成。输入分成10位,数据需预先编码,编码方式任意,但需保证有足够的跃变密度(每10位至少一次),使接收器锁相环能正确锁定相位,且编码需与传输介质兼容。

无论是编码模式还是直传模式,若处于空闲状态(时钟CKW上升沿时ENA=ENN=H),编码器将自动插入同步字K28.5(即C5.0)以保证接收器与发送器处在同步状态。

2.3 自检模式

BISTEL =1,收发送器工作于自检模式,7B923可分别发送两种信号来检测整个通信链路是否正常:一种是1与0相间的连续信号;另一种是循环发送的伪随机序列信号。若为后者,7B923输入寄存器转换成线性反馈移位寄存器LFSR,它可产生一组511个字节的伪随机代码序列,包括了所有的数据字和专用字。 7B933将输出寄存器也变成LFSR,产生与发送器相同的伪随机代码序列,并与接收的序列相比较。若相同,则整个通信系统工作正常,否则为异常,使 RVS=H给出错误信号。每次循环,7B923的RP及7B933的RDY都将输出一脉冲,此脉冲可用于记录循环次数以控制自检时间。7B923还可发送违规信号,以检测报错系统是否正常。这些信号都大大方便了故障诊断。

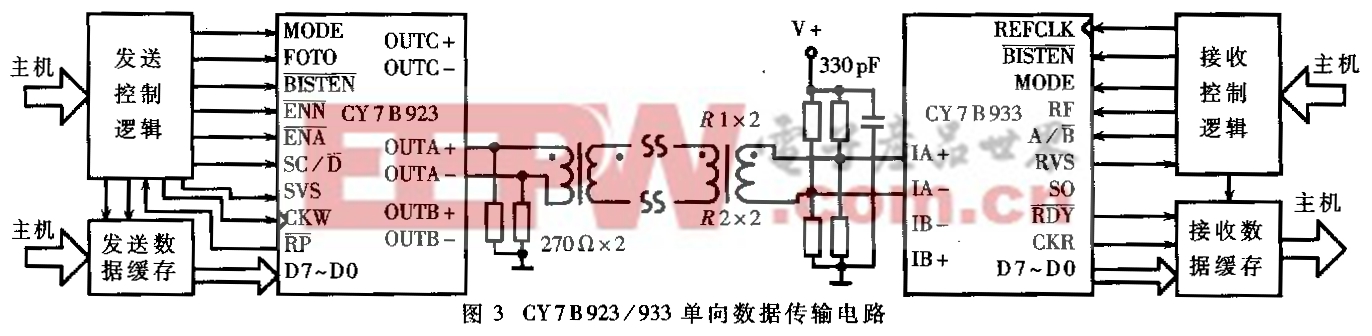

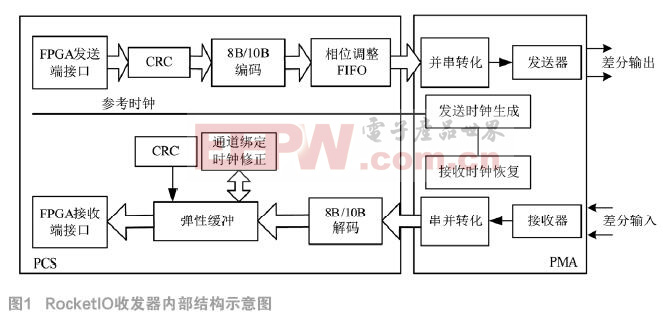

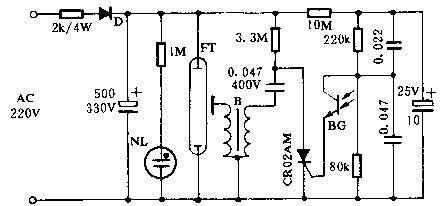

图3 为采用CY7B923/933实现的单向数据传输的应用电路。主机发送控制命令,通过控制逻辑控制CY7B923/933工作在传输或自检模式。这里控制逻辑用FPGA实现,也可采用其它数据逻辑器件实现。控制电路应包含RP、RVS端的检测,以判断系统工作正常与否,及时进行错误处理。主机数据传输速度一般与CY7B923/933不一致,发送端及接收端都需设置数据缓存,缓存一般用FIFO,我们采用CYPRESS公司的CY7C45系列,它可与 CY7B923/933组成无缝接口。若用FIFO的标志位作控制信号,则应注意标志延迟时间。CY87B933的输出信号CKR,可作为其输出数据写入 FIFO垢时钟,RDY可作写FIFO使能信号,使用RDY的优点是同步字串到它无效,自动滤除同步字串,这就保证了只将有奖惩数据写入FIFO,避免同步字将FIFO填满。电路板设计应采用四层板,CFY7B923/933的位置应靠近双绞线接口使连线最短,连线长度应尽量保持对称。输出输入端都应接匹配电阻,如图3所示。R1、R2阻值由下式给出:R1=(VccRt)/Vtt;R2=(VccRt)/(Vcc-Ctt)。式中,Rt为传输线阻抗;Vtt=Vcc-2V。Vcc=5V,UTP双绞线阻抗为100Ω,则R1=183Ω,R2=275Ω。

作者在一VME总线长距离高速点对点串行通信系统中,采用最大数据传输率为330Mbps的标准CY7B923/933ey UTP双绞线,实现了400Mbps的串行数据传输,工作稳定可靠,误码率小于10 -10。该工作是在中科院高物理研究所过雅南研究员、赵棣新研究员的指导下完成的,在此表示衷心地感谢!

评论