JPEG 2000标准中MQ编码器的VLSI结构设计

3 实验结果及分析

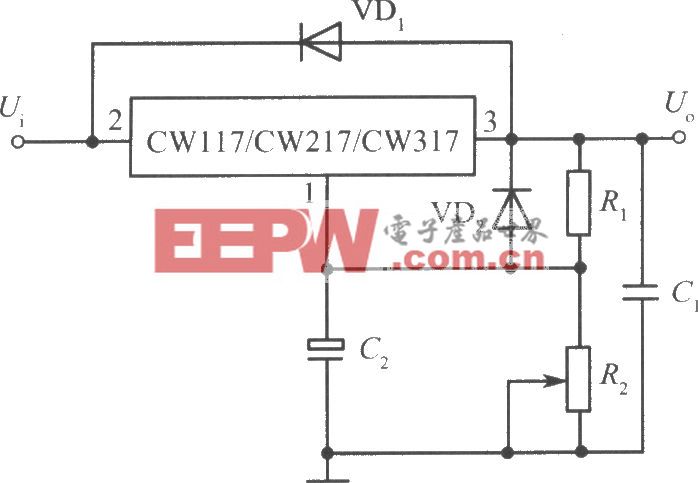

对所实现的MQ编码模块用Verilog HDL硬件描述语言进行RTL级描述,在Xilinx ISE 7.1和:Model-sim 6.1平台下进行功能验证和时序仿真。按字节输入测试码流:00 02 00 51 00 00 00 C0 03 52 87 2A AAAA AA AA 82 C0 20 00 FC D7 9E F6 BF 7F ED 90 4F46 A3 BF,得到结果码流为:84 C7 3B FC E1 A1 43 0402 20 00 00 41 0D BB 86 F4 31 7F FF 88 FF 37 47 1ADB 6A DF FF AC。得到的结果与理论结果一致,仿真波形如图4所示。

图4中D为输入的测试码流,CDH为输出码流。该设计在Xilinx的XA2C32A-6VP44器件上进行验证,结果表明,最高工作频率可达95.47 MHz,较大地提高了编码速度,能够满足JPEG 2000对高速编码的要求。

4 结 语

综上所述,为了满足现在对JPEG 2000高速编码的需求。在对MQ编码器的流程及相关算法进行分析后,利用现有FPGA的优势,在采用三级流水线结构的同时,对编码进行了优化;经 Xilinx的FPGA器件实现,不仅验证了该设计在功能上的正确性,同时表明在编码速度上得到了很大的提高,且最高工作频率可达95.47 MHz。

评论