JPEG 2000标准中MQ编码器的VLSI结构设计

2 MQ编码器的优化

MQ编码器采用串行执行方式,且编码算法复杂、耗时,从而导致编码器执行速度慢,效率低下。为了提高MQ编码器的运行速度,利用FPGA的大容量和并发执行等特性,对MQ编码器进行设计,在不改变原算法理论的条件下,对整个流程进行改进和优化。

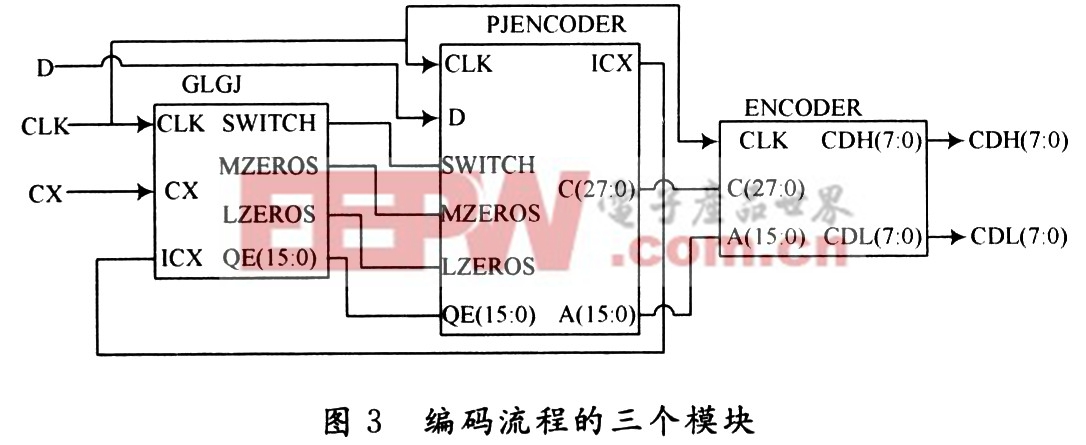

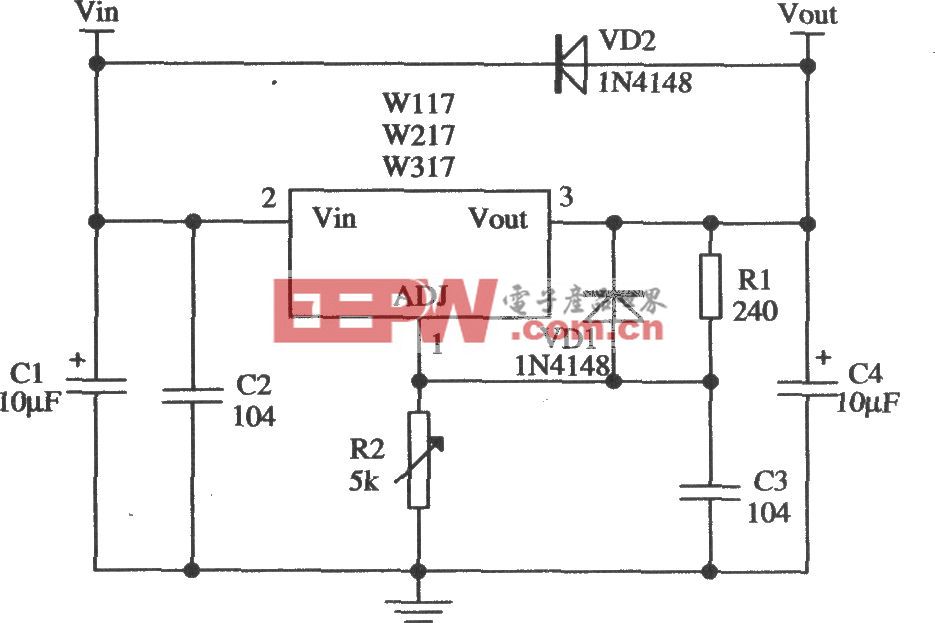

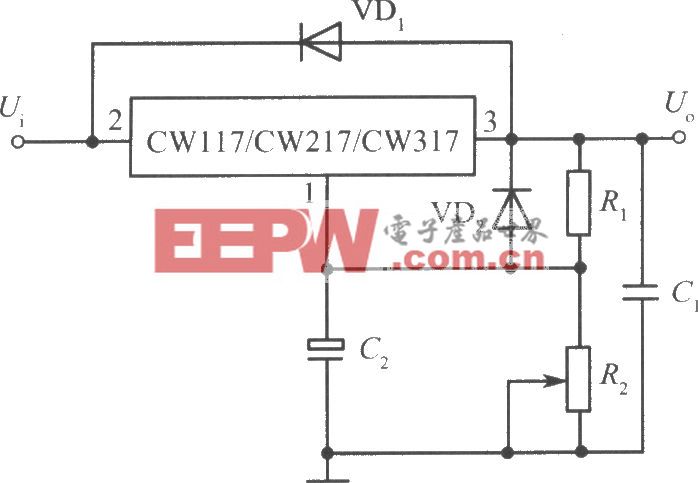

只有当前一输入的结果被输出后才能读人下一输入的串行执行方式,极大地限制了编码速度的提高。为解决这个问题,将整个编码流程分成三个大的模块(如图3所示)串接起来,采用流水线的方式进行工作。

其中,GLGJ模块为概率估计模块,其功能是根据上下文索引CX选择,判决D编码所必需的概率估值和相关数值,在各个上下文自适应更新数值; PJENCODER模块为判决编码模块,其功能主要是进行MPS编码或LPS编码、重新归一化等主要数据处理进程;ENCODER模块为编码输出模块,主要完成压缩数据的输出及编码终结等功能;由这三个模块组成三级流水线。

2.1 判决编码的化简

判决编码中先判断D的取值是“0”还是“1”,如果D=0,就进行0的编码;如果D=1,那就进行1的编码。在“0”或“1”的编码中,又要根据MPS (CX)的取值,判断是进行MPS编码,还是进行LPS编码;在MPS和LPS编码中,先更新区间宽度A的值,即A=A-Qe[I(CX)],再判断A是大于还是小于Qe[I(CX)],由此与其他的一些条件决定最后的赋值方式。

上述过程包括ENCODE,CCOE0/CODE1,CO-DELPS/CODEMPS五个子流程,6个条件判断,多次赋值,降低了编码速度。对编码的判决条件进行整理,减少不必要的赋值,其Verilog代码如下:

由此可有效地减少不必要的寄存器和位数赋值,加快模块的工作效率,从而提高整个系统的工作频率。

2.2 重新归一化的加速

MQ编码器一方面在编码MPS时,给代码C加上Qe值,将概率区间A减为A-Qe;另一方面,在编码LPS时,代码C不变,将概率区间A置换成Qe。如果将这样的区间划分运算进行下去,在某一时间点上,概率区间A就会比必要精度范围(O.75≤A1.5)小,这时就要通过重新归一化A与C维持精度范围。

重新归一化过程是根据条件(A0.75):当条件成立时,将区间寄存器A和代码寄存器C再左移1次,使其大小加倍,直到概率区间A的大小超过0. 75。由此可见,如果A的值很小,则左移操作将会反复进行,大大降低了编码速率。同时因编码中有MPS编码和LPS编码两种,根据D的不同以及编码方式的不同,重新归一化时移位的次数也不同。

因此为了提高速度,并充分利用硬件的优势,将Qe的移位次数作为寄存器数,加入到概率估计表中(表1所示)。无论输入数据D为何值,编码的判决都是以 LPS或MPS为标准,所以当判决为LPS编码时,LZE-ROS中的数据就决定了左移位的次数;当判决为MPS编码时,MZEROS中的数据就决定了左移位的次数。通过编程将扩展后的概率估计表,以寄存器的方式固化在芯片内部,虽然这样增加了硬件电路中寄存器的数量,但可以通过一次性的直接查表得到判决编码和重归一化所需的数据,提高了查找效率。由于每次编码都要用到该表,访问效率很高,这样大大加快了编码的速率,同时便于流水线结构的实现。

2.3 编码输出模块的改进

标准MQ编码器中当输出计数器CT=0时,MQ编码器输出1个字节。标准中字节输出流程是串行执行的,造成效率低下。又由于重新归一化过程采用了一次性的移位方式,最大的移位次数可达15次,且过程中伴随着字节输出。有三种可能情况:不需要进行字节输出,需要进行1个字节或2个字节的字节输出。因此需要对字节输出机制作改进。这里将减法记数器CT改为5位的加法记数器,并使用一个16位的数据缓存器。根据CT的取值,判别输出的是0字节还是1字节或者2字节,由此达到加速字节输出的目的。

评论