基于DSP Builder的Chirp信号源设计

根据Chirp函数在频域上的性质,可以得出输入控制字与输出频率之间的对应关系有线性和非线性两种:本文引用地址:http://www.eepw.com.cn/article/188609.htm

![]()

首先采用DSP Builder库中的单步增/减子模块(Increment/Decrement Block)建立采样点控制字产生单元。该模块能按照阶梯式规律步进逐一产生控制字信号,并保持一段时间在模块设置项(Clock Phase Se-lection)中设置,当增减方向(Direction)设置为Incre-ment时得时域输出,其表现如图7所示。

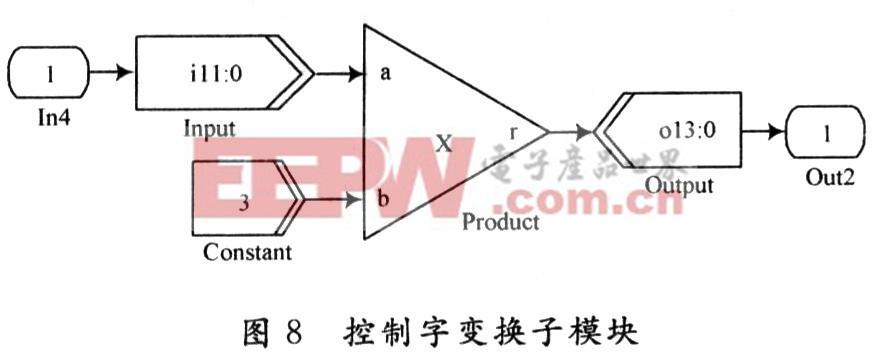

其次根据需要建立控制字变换模块,即对Incre-ment/Decrement模块输出的采样点控制字进行换算,转化为DDS的频率控制字。这需要根据不同Chirp函数的变化规律,例如:如果是线性频率的输出,则采样点应该与输出频率有线性的函数对应关系;如果是非线性频率的输出,则采样点应该与输出频率有非线性的函数对应关系。根据不同的传输函数建立该子模块:

例如:fout=kn+f0。当k=3时,建立子模块如图8所示。

将上述模块向上生成子模块后,连接的整体仿真如图9所示。

并在DDS的输出端建立FFT观测窗口。

4 验证与仿真

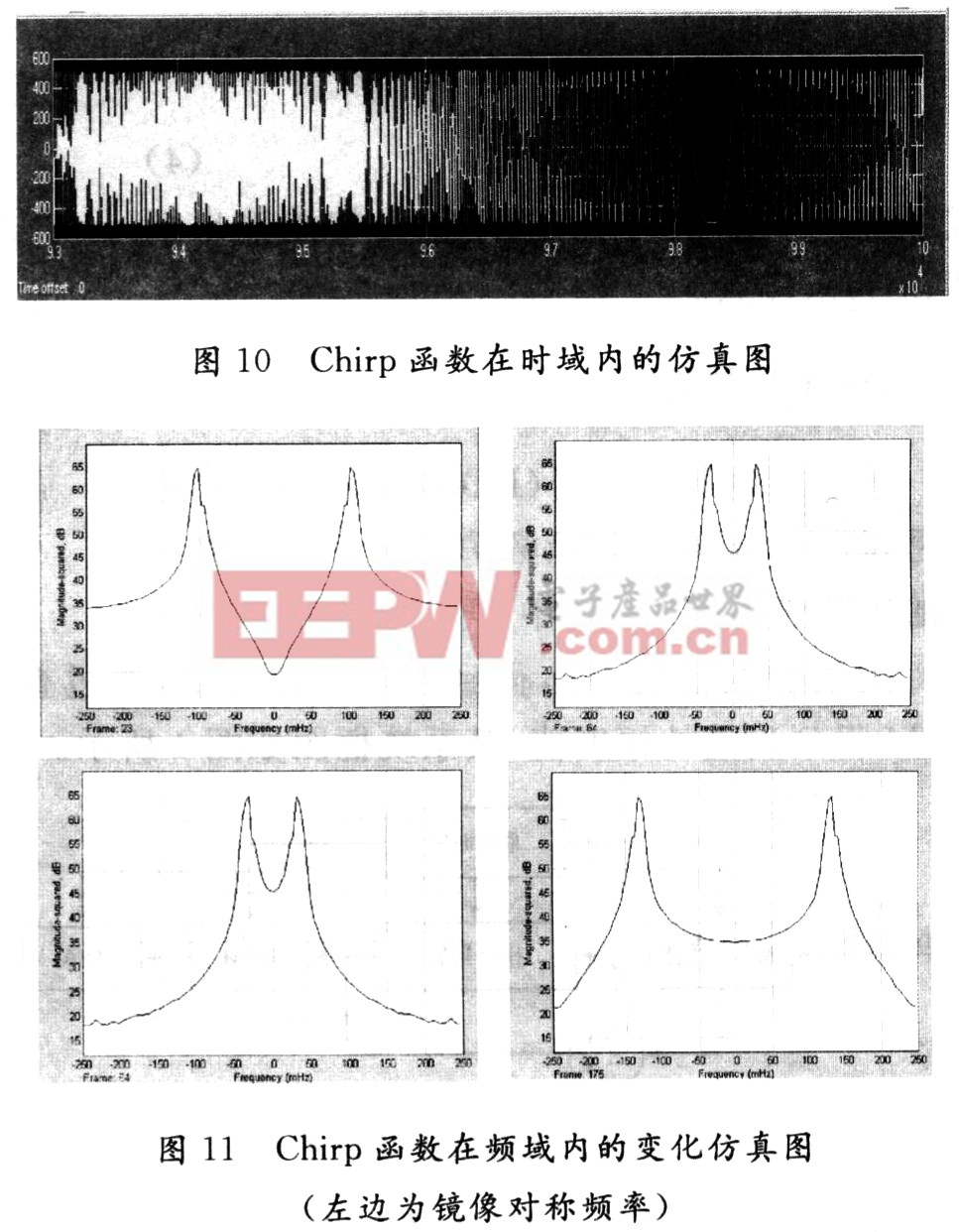

假设现在的初始相位为0,初始频率也为0,采样点步进控制字设置为输出12为步进循环增加模式。在时域输出观测窗口(Scope)中观察到图形如图10所示。

从图11中可见,输出信号的频率发生了周期性并且有规律的变化,证明了该设计能很好地实现Chirp信号源的功能。并且通过Altera DSP Builder提供的SignalComplier工具,能很轻松地生成HDL(VHDL或者Verilog HDL)代码下载到FPGA中运行,大大简化了FPGA设计。

5 结 语

根据Chirp函数特定的输入/输出(线性和非线性)关系,计算得出当前输入字与输出频率的对应关系,然后设计控制字子模块产生DDS模块的频率控制字,驱动DDS产生不同的输出频率,通过在Matlab的Simu-link环境下的仿真验证,得出不同时刻输出的频谱图,验证了该设计能很好地实现Chirp信号源。

评论