具有PCI和并行接口的数据采集系统设计

1 引言

本文引用地址:http://www.eepw.com.cn/article/188333.htm随着计算机技术的飞速发展和普及,数据采集系统也迅速地得到应用。在生产过程中,应用这一系统可对生产现场的工艺参数进行采集、监视和记录,为提高产品质量、降低成本提供信息和手段。典型数据采集系统的构成是由A/D+DSP+FPGA(CPLD)+D/A。本文通过利用模数转换芯片AD6644,以及FPGA实现了可用于两种接口(PCI、并行接口)传输模式下的高精度数据采集系统。

2 硬件电路设计

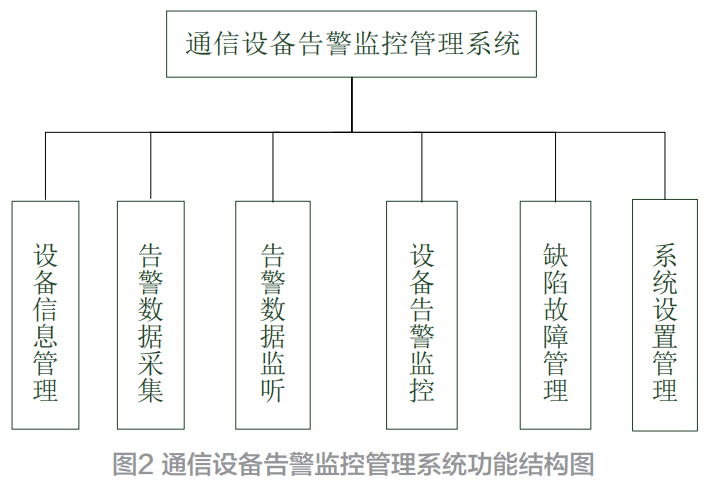

2.1 系统设计方案

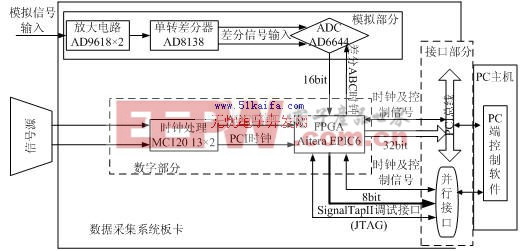

本数据采集系统主要由模拟部分,数字部分和接口部分三大板块组成,如下图1所示。其中模拟部分主要包含模拟中频信号预处理模块和模数转换模块;数字部分除时钟产生电路外,其余部分完全在FPGA中设计完成;接口部分包含PCI总线接口、DB25并行接口以及SignalTapII逻辑分析仪调试接口。

本系统的设计思路就是:首先通过模拟中频信号预处理模块,将调整后的模拟信号输入给A/D转换器,然后经模数转换之后将16bit数字信号(AD6644输出14bit,再加上2个校验位)直接输出给FPGA进行存储。在FPGA中设计了高速缓冲器DCFIFO和高速存储器DPRAM以及一系列时序控制逻辑,以保证在预定容量下能够实时的存储由ADC发送过来的数据。同时,在FPGA中还设计了2种数据传输接口,从而使得系统可以在我们选择的模式下进行数据传输,或通过并行接口,或通过PCI总线接口。

图1 系统总体框图

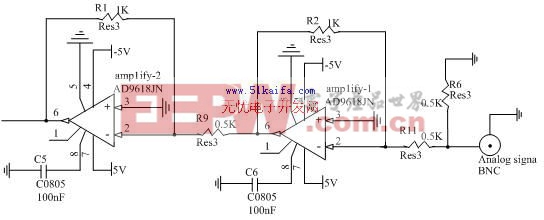

2.2 模拟中频信号预处理模块

首先,将该输入信号通过两级放大器,目的是为了使模拟输入信号幅度达到AD6644输入幅度的要求和对模拟输入信号进行很好的隔离。这里选用AD9618来实现对模拟信号的放大功能。AD9618的单位增益带宽和压摆率的指标均较高,能起到对模拟输入信号放大和改善性能的作用。电路图如图2所示。

图2 两级AD9618放大器原理图

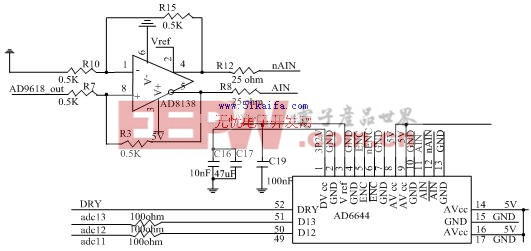

其次,将经过放大处理后的单端信号通过AD8138,转换为差分信号后输出给AD6644。这么做是因为作为新型的高转换速度、大动态范围的ADC,为保证其性能,AD6644的模拟输入信号要求差分形式。在模拟信号阶段使用差分形式,可以有效地滤除偶次谐波分量,同时对其它共模杂散信号(如由电源和地引入的噪声)及对晶振的反馈信号也有很好的抑制作用。如下图3,使用AD8138对模拟信号进行调整。单端模拟信号(AD9618_out)由AD8138转换为差分模拟信号(AIN、nAIN),增益为1,然后送AD6644实现模数转换。AD8138的直流偏压VREF由AD6644的精密参考源提供。采用差分输入比单端输入大约可以提高信噪比3dB。

2.3 FPGA配置与模数转换模块

FPGA部分是本系统的核心模块,承载了所有的数字电路部分。在设计过程中,强调SOC(片上系统)的概念,在FPGA平台上实现了系统中所需要的所有数字逻辑,包括触发器、存储器,缓冲器,PLL(锁相环),计数器,译码器,多路选择器,DB25接口逻辑,PCI接口逻辑等。从而使得系统中的数字部分处于完全可编程可调状态,只需根据需求更新FPGA程序即可,具有较强的适应性和灵活性。基于上述思路,我们选择了Altera公司的Cyclone系列FPGA――EP1C6Q240C8。

图3 AD8138+AD6644连接原理图

在本系统中,使用了2种配置方式,即AS方式和JTAG方式。这2种配置方式可以共同使用,只需在板子上放置2套接线柱即可,下载电缆采用ByteBlaster II。首先使用JTAG方式配合Quartus II工具中自带的在线逻辑分析仪SignalTap II对FPGA功能及时序进行调试,成功后再使用AS+EPCS4方式将程序下载到配置芯片EPCS4中,使得每次系统上电后,都能对FPGA自动加载程序。另外要注意,使用这种配置方式时,如果让JTAG和AS模式同时开始加载,则JTAG模式会自动取得优先权进行程序加载,而AS模式则会自动终止。

评论