基于HSP50214B的侦察接收机数字解调模块设计

3 数字解调模块原理

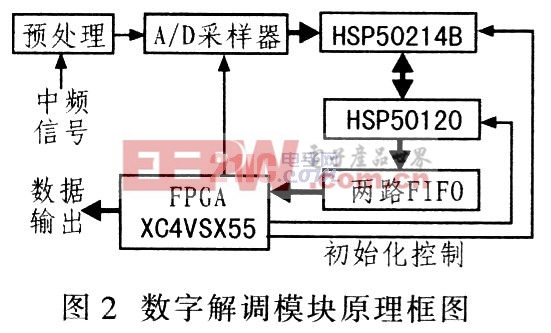

侦察接收机中实现数字中频滤波技术,数字下变频器是关键部分,它将中频信号搬移到基带为后续信号处理做准备,并同其他器件构成数字解调模块,图2为其原理框图。

中频信号经放大器、带通抗混叠滤波器、模拟AGC等预处理过程。再送至A/D采样器进行中频带通采样,采样信号通过HSP50214B实现数字下变频和抽取,同时利用HSP50210提取相干载波、码元同步信号和载波跟踪情况指示,实现载波同步和码元同步,最后将抽取信号送至FPGA进行数字信号处理,解调输出结果。整个模块在FPGA的控制下实现数字下变频、码速变换、信道化、时钟回恢复、解调、解扩等功能。HSP50210可编程数字科斯塔斯环专用电路,其时钟处理速率达52 MHz;FPGA采用Xilinx公司的VIRrrEX4系列器件XC4VSX55实现其所有功能,该器件具有24 576个逻辑单元,内含丰富的存储单元(共5 760 Kbit),具有用于多种运算的IP核,特别适用于实现高速信号处理,其并行处理性能优于传统的DSP处理器。

4 HSP50214B的电路设计及接口配置

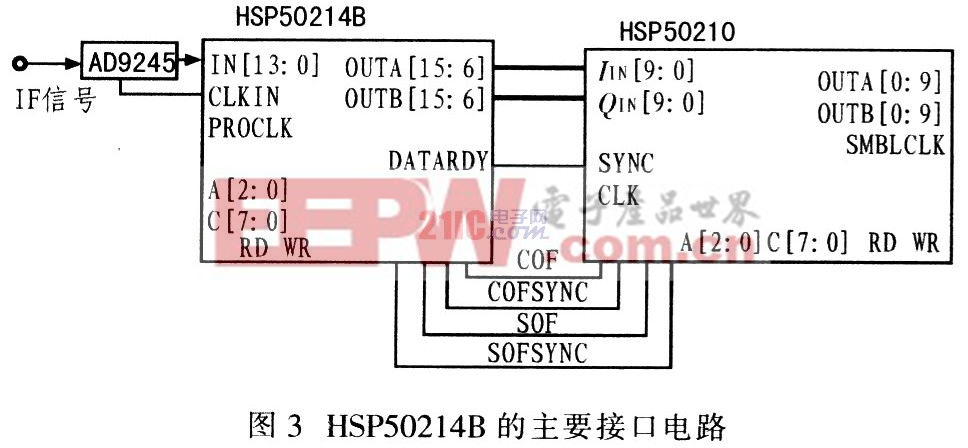

同HSP50214B直接相连器件的主要有:AD9245、HSP50210和XC4VSX55。图3为数字下变频器HSP50214B的主要接口电路。

经前端预处理的模拟中频信号(IF信号)传送至A/D采样器进行采样。A/D采样器采用AD9245,其输出为14位,最高采样速率可达80 MHz,输入范围大,功耗小,性价比较高。由于HSP50214B的输入为14位,因此将AD9245的14位输出接到HSP50214B的14位输入即可。HSP50214B的CLKIN引脚与AD9245的时钟相连。每个CLKIN信号到达就对其输入数据采样1次。CLKIN的时钟信号可达65 MHz,PROCLK时钟是混频后的处理时钟,最高不能超过CLKIN时钟。

将HSP50214B设置为并行直接输出模式,输出的数据是I、Q两路正交分量,16位并口OUTA [15:0]输出同相分量,OUTB[15:0]输出正交分量。由于HSP50210只有10位输入,取HSP50214B的高10位输出数据OUTA[15:6]、OUTB[15:6]分别接入HSP50210的输入端口IIN[9:0]、QIN[9:0]。NSP50214B的DATARDY引脚与HSP50210的SYNC引脚相连,当OUTA端口有新的数据产生时,HSP50210响应DATARDY同步信号,分时并行接收数据,依次在下变频器的OUTA和OUTB两个输出端处接收同相与正交分量。数据的读取、写入、寄存器选择等控制信号通过FPGA电路控制,WR和RD用于控制其读写控制字的控制信号,通过FPGA的嵌入式PoweiPC发出并送入其端口:8位控制接口数据总线C[7:0]接P00~P07,3位寄存器地址线A[2:0]接P12~P10。

评论