正弦信号发生器设计方案

本文引用地址:http://www.eepw.com.cn/article/188251.htm

4 主要功能电路设计

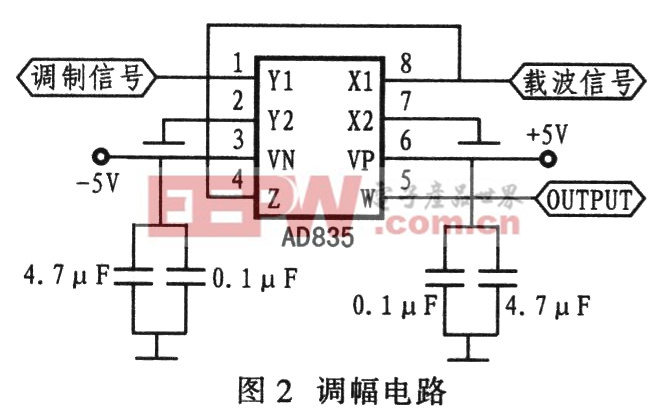

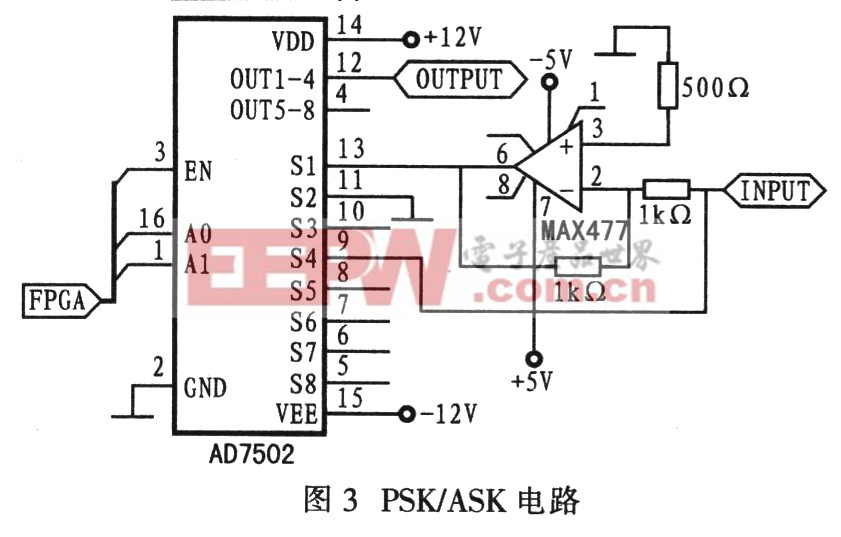

图2给出调幅电路。它采用ADI公司的乘法器AD835实现。该器件内部自带加法器,可直接构成调幅电路。图3给出PSK/ASK电路。它主要由多路复用器和移相器构成。其中,移相器采用Maxim公司的高速运算放大器MAX477所构成的反相放大电路实现,多路复用器采用ADI公司的AD7502。当两条通道选择控制线A1AO为ll时,输出原信号;当A1A0为00时,输出原信号的反相信号;当A1A0为01时,无信号输出。这样只要FPGA按固定速率通过Al和AO两条控制线给出基带序列信号,就能相应输出PSK和ASK信号。

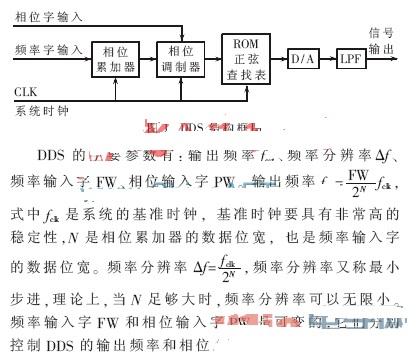

FPGA内部DDS调频电路由分频器、累加器、ROM和AD985l时序控制电路构成。分频器用于得到20 kHz的信号,作为AD985l控制字的切换频率;ROM中存储了1 kHz的正弦波表,接收累加器给出的控制字切换信号,同时向AD985l时序控制模块发送频偏控制字;AD985l时序控制电路根据中心频率并结合频偏控制字向AD985l器件发送频率控制字,以实现DDS调频。

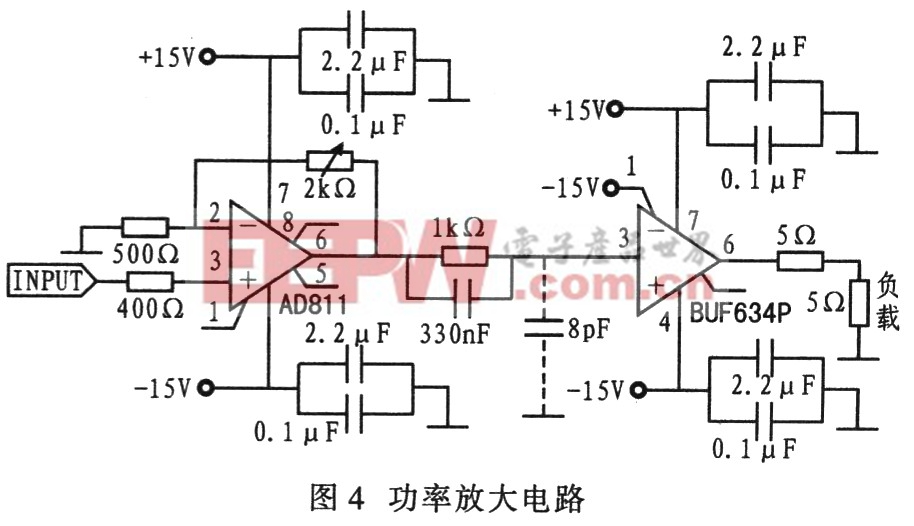

功率放大电路由ADI公司的高速运算放大器AD811和T1公司的缓冲器BUF634构成,如图4所示。AD8ll采用同相放大器接法,将输入信号放大到电压峰峰值为6 V;后级缓冲电路用于提供足够的输出电流,使负载的输出电压峰值稳定在6 V。由于AD81l的输出电流较大,所以在AD811与缓冲器之间串接了一只l kΩ的电阻用于限流。电路调试时发现.输出高频信号有衰减。经过分析获知,主要原因在于后级缓冲器有8 pF的等效输入电容(见图4中虚线),该电容影响电路的高频响应。于是在AD811输出与BUF634输入之间接入了一只330nF的补偿电容,补偿后的电路高频响应效果良好。

5 系统软件设计

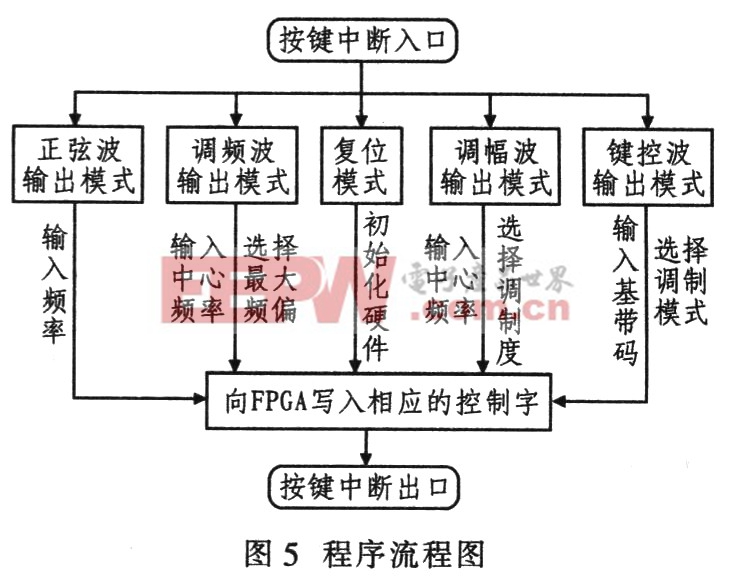

该系统软件采用结构化和层次化的设计方法。前者指相应的基本功能模块利用底层处理子程序所处理的数据,向上层全功能模块提供处理后的数据;后者指利用前者的接口完成该模块功能。最后由主程序调用全功能模块构建系统。图5给出程序流程图。

整个程序以按键中断为主线,分为正弦波、调幅波、调频波、键控波4种输出模式和1个复位模式。在不同的模式下分别执行相应的子程序,最后分别向FPGA写入相应的控制字。

6 测试数据

该系统测试主要由高频毫伏表、频率计、示波器完成。其中,高频毫伏表测试输出信号峰值;频率计测试输出信号的频率;示波器用于测试正弦波、调幅波、调频波、PSK以及ASK等信号波形。这里选取1 kHz,lO kHz,100 kHz,l MHz和10 MHz这5个频率点对正弦信号发生器进行测试,将实际频率与预置频率相比较,得到各频率点的相对误差均小于0.05‰。其中100 kHz和10 MHz处的相对误差小于0.02‰;5个频率点所对应正弦信号的电压峰值分别为6.28 V,6.25 V,6.10 V,5.90 V,5.60 V。

7 结语

该系统较好地完成了预期的各项功能和指标。正弦波的输出频率范围为l kHz~10 MHz,在其内频率稳定度为10~4;调频波的输出频率范围为100 kHz~10 MHz,在其内最大频偏可分为5 kHz/10 kHz二级程控调节;调幅波的输出频率范围为l~10 MHz,在其内调制度可在10%~100%之间程控调节,且步进为10%;ASK及PSK信号则通过移相电路和多路复用器的结合,在FPGA给出的基带序列信号控制下产生。

![[组图]精密的单电源光检测电路设计方案](http://uphotos.eepw.com.cn/fetch/20220926/59_97_17_0.jpg)

评论