基于CSMC工艺的零延时缓冲器的PLL设计

1 引言

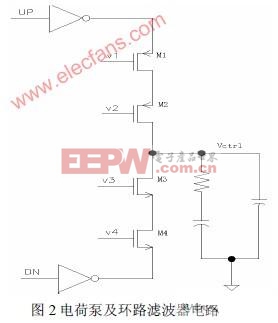

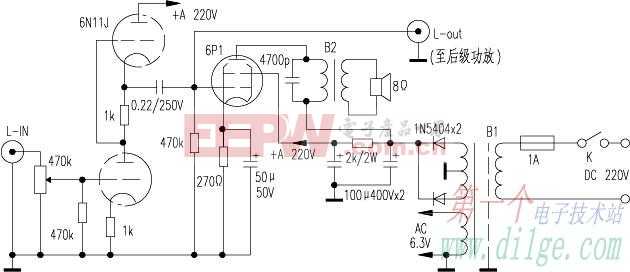

本文引用地址:http://www.eepw.com.cn/article/187824.htm本文在传统锁相环结构的基础上进行改进,设计了一款用于多路输出时钟缓冲器中的锁相环,其主 要结构包括分频器、鉴频鉴相器(PFD)、电荷泵、环路滤波器和压控振荡器(VCO)。在鉴相器前采用预 分频结构减小时钟信号在传输过程中受杂散分布的电容电感的影响,避免产生信号畸变、漂移等严重影 响电路随时钟精确工作的现象。PFD 比较两个分频器的信号,产生误差信号对电荷泵进行充放电,电荷 泵产生的模拟信号经过环路滤波器后调节VCO 频率。VCO 输出后的分频器的分频系数与预分频系数相 等,目的是使输出与输入的时钟信号频率相同,起到缓冲而不是分频的效果。锁定后实现输入与输出信 号零延迟。

2 电路结构

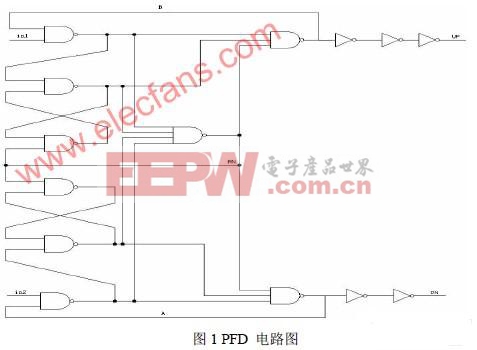

2.1 鉴频鉴相器(PFD)

PFD 产生关于频率和相位误差的信号,其脉冲宽度与相位误差成比例的变化,传输给电荷泵及环路 滤波器引起压控振荡器控制电压的变化,进而改变振荡频率。电路工作的进程如图2 所示,这是一个下降沿比较的结构,由两个基本RS 触发器和两个带复位端的RS 触发器组成。这种鉴相器不仅可以对相位 进行比较,也可以对频率进行比较,锁存结构记忆了前一次的输入信号状态,从而决定了下一次的输出 状态。

评论