四阶连续时间正交带通ΣΔ调制器的设计

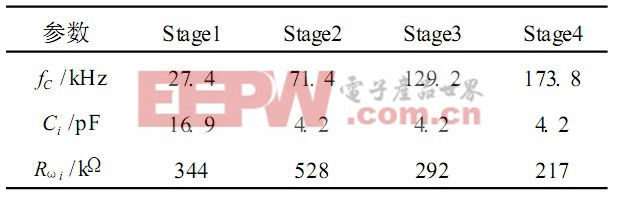

表1 调制器零点配置

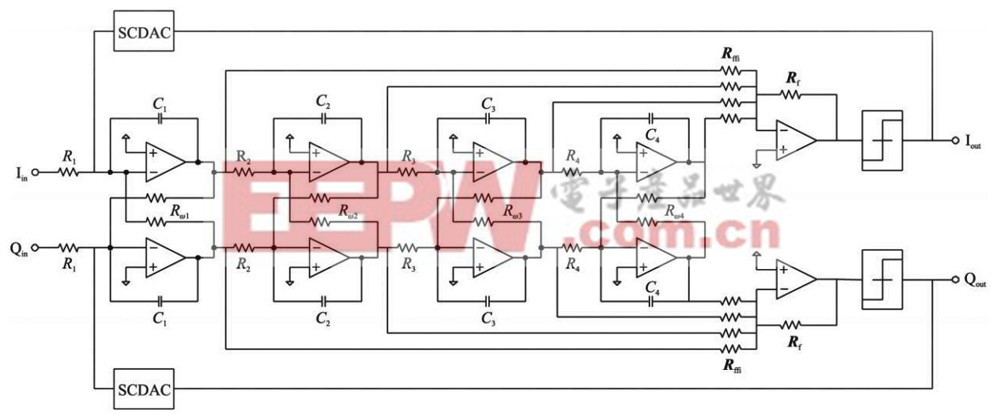

如图3所示,这是本文设计的四阶连续时间正交带通ΣΔ调制器,它由I、Q两路四阶前馈低通ΣΔ调制器经过电阻交叉耦合组成。

3 时钟抖动

时钟抖动是限制连续时间ΣΔ调制器性能的主要非理想因素之一。由于时序的不确定性,在量化器对求和电路输出进行采样和DAC产生反馈波形时都会引入误差。在采样过程中引入的误差和量化噪声一同被调制器的NTF整形。然而,DAC引入的误差直接反馈到输入,会限制整个调制器的性能。

采用开关电容反馈DAC能降低连续时间调制器的性能对时钟抖动的敏感度。

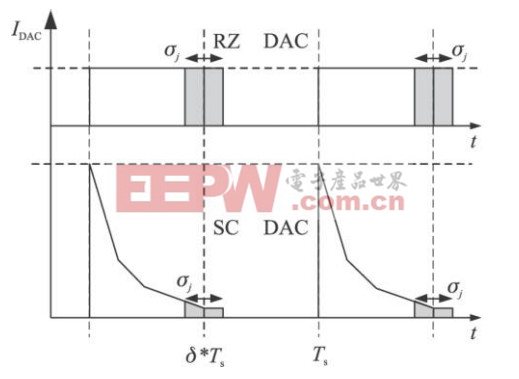

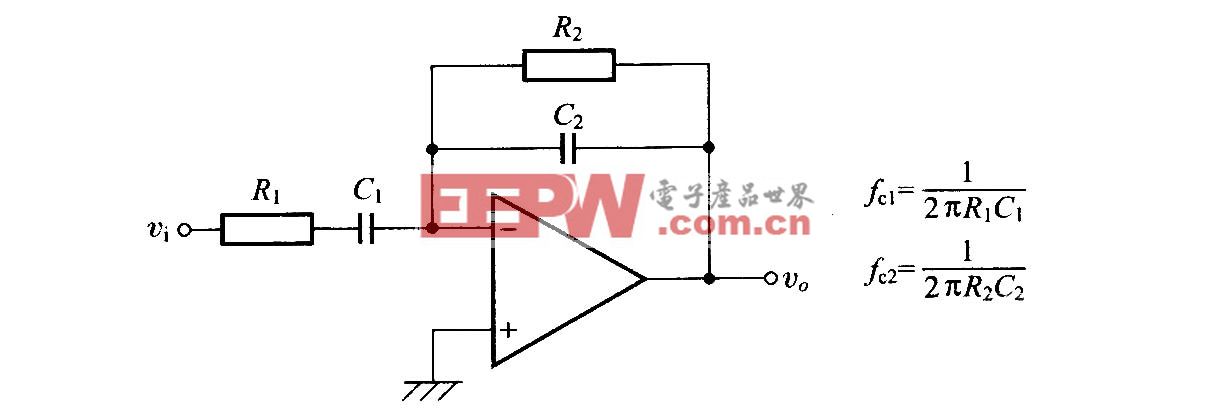

图4反映了时钟抖动对归零矩形波和指数波形的影响,在这两种反馈波形下,时钟抖动对SNR 的限制分别为:

其中,δ是DAC的占空比,σj 时钟抖动的均分根,α =TS / (RdacCdac )是采样周期与时间常数的比值,这里认为时钟抖动是方差为σj2 的随机白噪声。由(5)式,可以看出时钟抖动引入的误差与开关电容DAC的时间常数有关。比较以上两式,可以看出与归零矩形波相比,指数波形更能抑制时钟抖动效应对SNR的影响。

图4 时钟抖动的对反馈波形影响

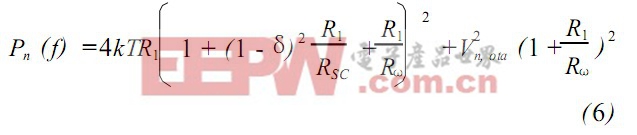

开关电容DAC的热噪声是调制器输入参考热噪声的重要组成部分,参考文献的结论,可以推出第一级复数积分器输入端的参考热噪声近似为:

其中RSC = TS /Cdac是开关电容电路的等效电阻。

评论