基于CPLD的TMS320F2812硬件平台设计

process(reset,xzcs2)

begin

if(reset=’0’) then

daccs=’1’;daca0=’1’daca1=’1’; --复位状态

--选通0xC0000~0xC0003

elsif(xzcs2='0' and a18='1' and a17=’0’ and a16=’0’ and a3=’0’ and a2=’0’) then

daccs='0';

case a1_a0(1downto 0) is

when 00=>dac_a1_a0=00;--选择A,B,C,D 数据保持通道

when 01=>dac_a1_a0=01;

when 10=>dac_a1_a0=10;

when 11=>dac_a1_a0=11;

when thers=>null;

end case;

--选通传送寄存器

elsif(xzcs2='0' and a18='1' and a3=’0’ and a2=’1’and a1_a0=”00”) then

daccs='0';

ldac=’0’;

end if;

end if;

end if;

end process;

2.2.2 串行非易失型存储器X25650芯片的应用

在这里,我们外扩了SPIOER 寄存器来控制DSP 与X25650 的SPI 接口,它的作用是连A18-A0XZCS2XWETMS320F2812XR/WD11-D0CSA0A1LDACDAC7625R/WDB11-DB0CPLD 译码逻辑daccsdaca0daca1DACTLR ldac图 2通或割断DSP 与X25625 的连接。当需要F2812 的SPI 接口与SPI515(SPI 接口型)仿真器连接,实现仿真操作时,可以通过寄存器屏蔽SPI 对X25650 的操作。SPIOER 控制寄存器的地址为0xC0002,使用了外部总线来对其进行读写,它的使用:

SPIOE 位:当SPIOE 位为“1”时,DSP 与X25650 各引脚接通;当为“0”时各个引脚断开,此时,DSP 上的SPI 引脚为高阻态,可以连接其他设备。上电复位时为“1”。该寄存器由CPLD 内部编程构成。

在 F2812 中,SPI 模块支持125 种不同的波特率,通过向波特率寄存器(SPIBRR)写入设定值,可以与不同速率要求的外设通信。其波特率设定如下:

当 SPIBRR=3-127 时, SPI 波特率=LSPCLK/(SPIBRR+1)。当SPIBRR=0,1,2 时, SPI波特率=LSPCLK/4在这里:LSPCLK=设备的低速外围时钟频率。SPIBRR=主SPI 设备中SPIBRR 的内容。

这里,通过配置低速外设时钟预定标器寄存器(LOSPCP)和SPI 波特率寄存器(SPIBRR)中的内容,使DSP 的波特率达到5MHZ,满足X25650 的要求。

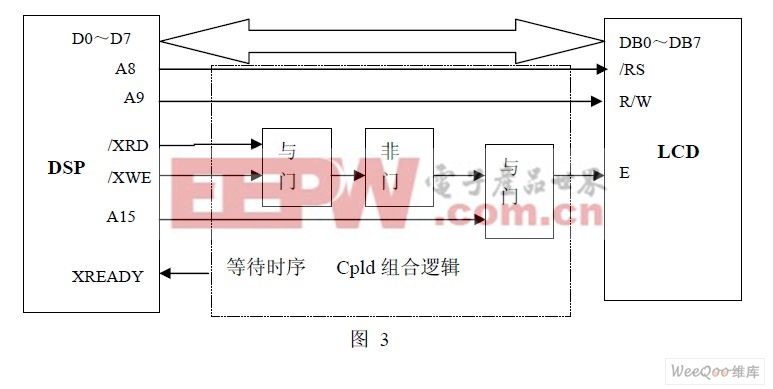

2.2.3 字符型液晶显示器的应用

本系统将字符型液晶显示器MDL(S)16263 作为DSP 的一个慢速显示设备,映射在XZCS6 区域。该模块共有11 条信号线,RS 是寄存器选择,低电平选择指令寄存器,高电平选择数据寄存器。R/W 是读写控制端,低电平写显示模块,高电平读显示模块。E 为允许输入信号线(数据读写操作允许信号),高电平有效。DB0~DB7 为数据线。

但是相比较 DSP 而言,LCD 是慢速设备,在设计器件时要考虑时序匹配问题,加入合适的等待状态。该液晶模块读写周期Tcyc 最小为1000ns,脉冲宽度Pw 最小为450ns,读写操作数据保持时间最小为10ns,而F2812 的XINTF 外设接口的读写访问默认情况下为最大值,为26 个XTIMCLK 周期(XTIMCLK 默认为SYSCLK/2,13ns.),也就是说最大读写周期为346ns,其中读或写访问的建立阶段默认为6 个XTIMCLK 周期、激活阶段默认为14 个XTIMCLK 周期、跟踪阶段默认为6 个XTIMCLK 周期。因此,读写周期需要加入等待状态。

当对DSP 的XREADY 引脚采样为低电平时,激活阶段将扩展一个XTIMCLK 周期,在下一个XTIMCLK 周期期间,XREADY 再次被采样。这一个过程一直被采样,直至XREADY采样为高,正常地完成访问。这里,我们利用CPLD 芯片将DSP 的XREADY 信号置为低电平,保持50 个XTIMCLK 周期,从而产生合适的等待状态。如图3 所示:

3 结论

本系统的开发采用了 DSP+CPLD 的结构,这种结构将DSP 较强的数据运算能力与CPLD 的高集成性、硬件可重复编程性结合在一起,使系统的设计过程更加的合理、紧凑和简化。并且,该系统经过扩展后可以应用在工业控制的多种场合,具有一定的实际参考价值。

评论