H.264编码器中亚像素运动估计的硬件实现

图4 菱形全搜索

即先利用整像素运动估计搜索出最佳整像素点,再在最佳整像素匹配点的基础上搜索出最佳整像素点周围的36个亚像素点(假设在图5中正中心点是最佳整像素匹配点)。等36个亚像素点都计算出来后,加上正中心的最佳整像素点共37个像素点。比较这37个像素点的SATD的值,将SATD值最小的像素点确定为最佳的预测点。

由于H.264采用树形结构运动估计,每个宏块可划分成更小的子块,其中4×4块是宏块划分中最小的子块,任何类型的子块都可由若干个具有相同运动矢量的4×4块组成,因此本设计在硬件实现时将4×4块作为处理的基本单位。考虑到硬件资源的节省及计算的并行度,在本设计模块中每次能并行处理两个4×4块的亚像素点的搜索,一个宏块(16×16)要分8次完成。

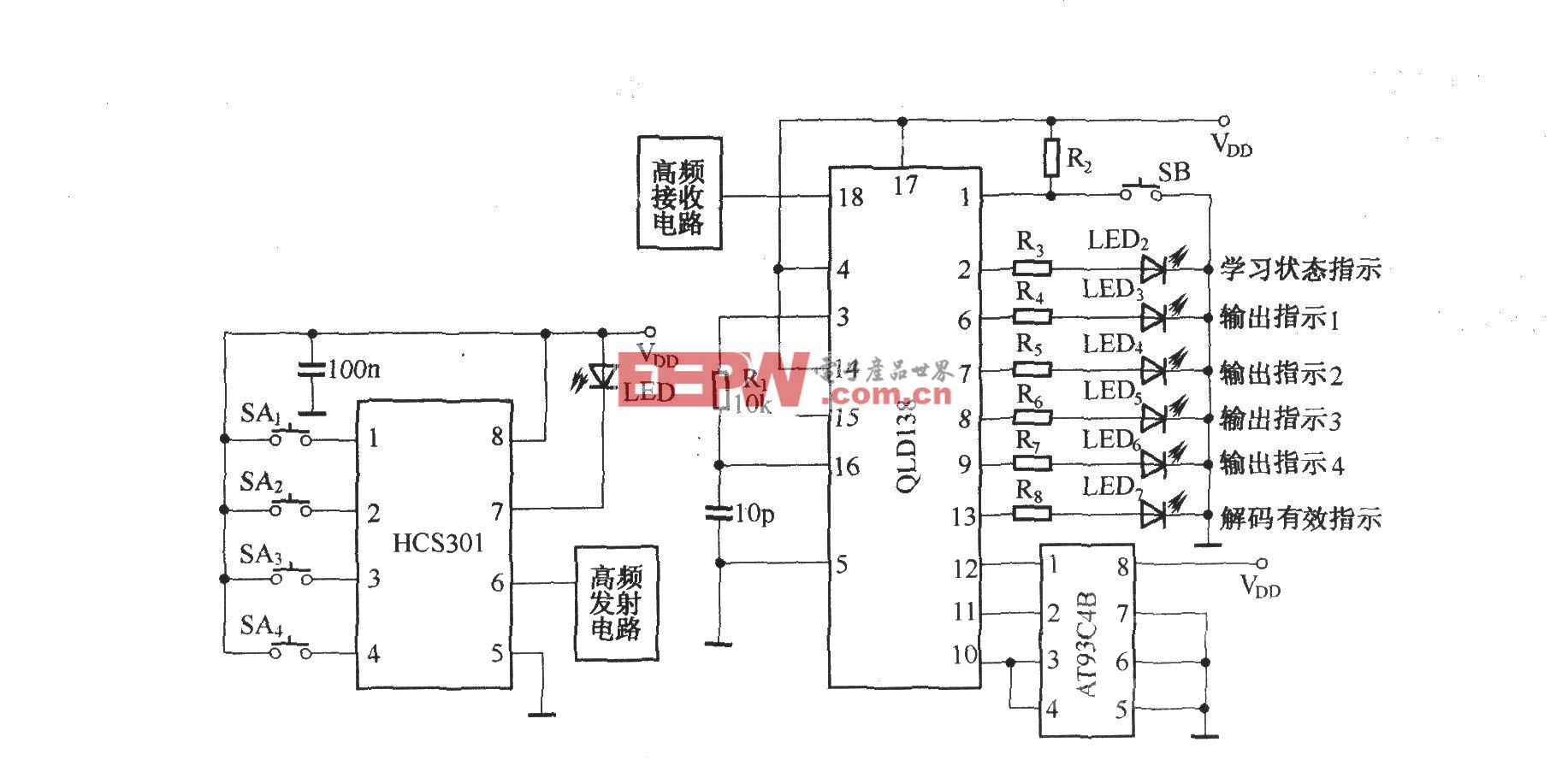

其中IME单元为FME单元提供10×10整像素点阵列,内插法用于1/2像素点的插值,ave单元用于计算1/4像素精度的像素点,Sram单元用于存储计算出来的亚像素点的值。比较器单元由diff、DCT、satd三个单元组成,用于比较这些亚像素的SATD值,确定最佳的亚像素预测值。

假设当前处理的4×4块在参考帧中的最佳整像素匹配块(4×4块为匹配的块),在硬件实现的过程中为减少搜索次数,只要搜索出图5中对应的5×5块的每个整像素点左上角的15个亚像素点(,然后将相邻整像素点左上角的亚像素点进行组合后就能将当前处理的4×4块中每个整像素点周围的36个亚像素点都计算出来。

图5 最佳整像素匹配块

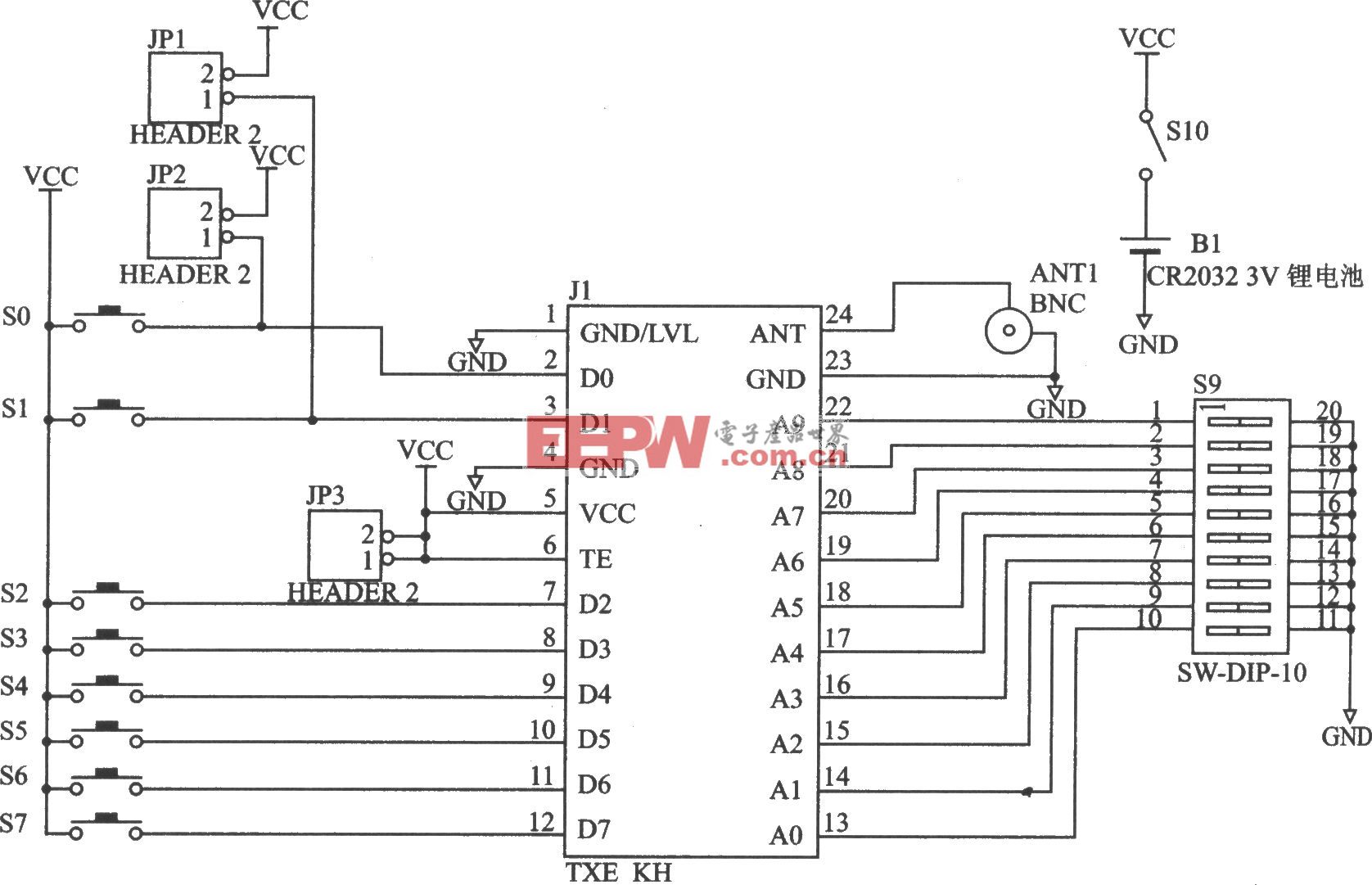

本设计在硬件实现的过程中为提高计算的并行度,利用15个六抽头滤波器,25个均值器等硬件资源来计算图8所示的亚像素点的值,计算依据分别如公式1、2所示,硬件搜索计算过程如图6所示。

图6 亚像素点硬件搜索步骤

通过上述15个步骤就可将图8所示的亚像素点全部计算出来,并将计算出来的亚像素点的值都存入到开辟的Sram中,以便在进行P帧重构时从Sram中直接取出最佳的预测值给相关的模块。由于如上文所述在对每个4×4块进行亚像素搜索时要计算出对应的5×5块(如图7所示4×4块对应的5×5块)的每个整像素点左上角的15个亚像素点的值(如图8所示的15个亚像素点),加上最佳整像素点共16个像素点的值都要存储起来,且对应的5×5块中的每个整像素点左上角的亚像素点的像素值都是并行计算出来的(如step1计算点2,是将对应的5×5块的25个整像素点左上角对应的点2一次全计算出来),所以在进行一个4×4块的亚像素搜索时,要存储的像素点共有25×16个。由于在本设计模块中每次能并行处理两个4×4块单元,即利用两套FME模块资源并行处理两个4×4块的亚像素搜索,一个宏块(16×16)要分8次完成。考虑到数据组织的方便性,本设计在一套FME模块中开辟两块Sram资源,一块大小为104×128,一个地址存储13个像素点的值(每个像素点的值占8bit),另一块大小为96×128,一个地址能存储12个像素点的值(每个像素点的值占8bit),地址深度128刚好能存储8个4×4块的亚像素点的像素值,所以两套FME模块中的Sram资源刚好能把一个宏块的亚像素点的像素值都存储起来。此设计在硬件的实现过程中计算并行度高,硬件实现简洁有效。

根据图6所示的硬件架构及上文描述的算法原理,利用Verilog HDL对其进行建模,建立测试平台在ModelSim环境中进行编译、仿真,验证其功能的准确性。然后使用Synplify工具对其进行综合,工作频率可达68MHz。在FPGA 验证平台上,可实现对高清码流(1920×1080)的编码,利用Design Complier工具进行综合,在中芯国际0.18μm 工艺标准单元库的基础上,综合后面积占150千门,工作时钟频率可达166MHz,达到了预期要求。

结语

H.264中的分数运动估计能有效提高预测精度,但大大增加了计算复杂度。同整数运动估计一样,分数运动估计存在两个主要问题,一是计算量大,二是存储访问量大。而本文提出与其他实现方法相比在空间上具有更高的并行度,处理能力更高,不但减少了大量中间数据的存储与传输,节省了存储器资源,而且简化了数据流和控制流,使硬件实现简洁有效,非常适合高分辨率视频的分像素运动估计。

评论