基于DP标准发射端扩频时钟发生器电路设计

引言

本文引用地址:http://www.eepw.com.cn/article/187197.htmDP(DisplayPort)接口标准旨在寻求代替计算机的数字视频接口DVI、LCD显示器的低压差分信号LVDS(Low Voltage Differential Signal)。DP利用目前交流耦合电压差分的PCI Express电气层,有1~戽个工作速率为217 Gb/s的数据对(Lanes),最高可获得4通道多达10.8 Gb/s的带宽。时钟不是分离的,而是内置于Lanes。传输命令和控制的辅助数据通道是双向的,最高传输比特率可达1 Mb/s。DP支持的最大传输距离为15 m,而其工作电平比DVI更低。

伴随微处理器的频率不断增加,由此产生的电磁干扰会影响电子产品的正常。为了抑制电磁干扰,人们先后研究出屏蔽、脉冲整形、滤波、低电压差分时钟、特殊版图布局、扩频时钟发生器等方法,其中扩频时钟发生器可有效减小峰值和谐波的功率,且可通过电路设计的广阔空间实现,因而得到广泛应用。这里设计一种基于DP标准采用μ工艺的发射端扩频时钟发生器。合理设计锁相环路,采用外加滤波器对压控振荡器的控制电压进行三角波调制,得到所需的扩频时钟。

2 扩频时钟发生器总体结构

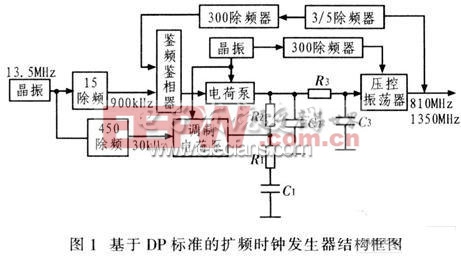

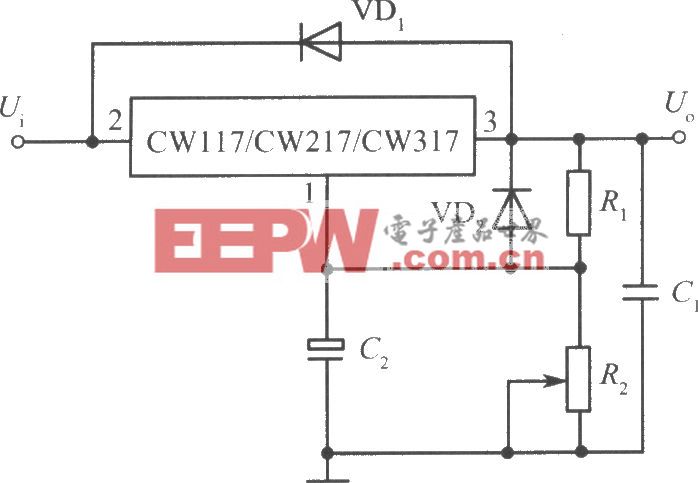

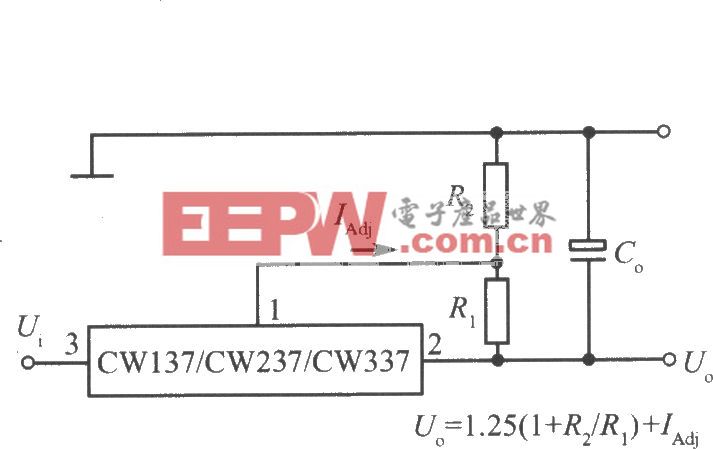

降低电磁干扰(EMI)是电子系统设计人员需要考虑的重要因素,扩频时钟(CLK)为降低EMI提供一个有效途径。这里采用tsmc0.18μm 工艺设计一款符合DisplayPort标准发射端的扩频时钟发生器。在合理设计锁相环路的基础上,运用外加电荷泵对压控振荡器的控制电压进行三角波调制,得到所需要的扩频时钟。图1为该设计结构框图。

3 各模块电路设计

3.1 鉴频鉴相器电路

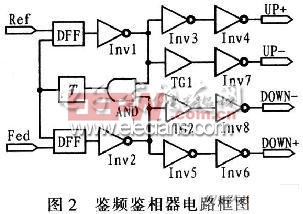

图2为鉴频鉴相器电路框图。鉴频鉴相器的输出由输入信号的频率和相位决定,它比较两个输入信号的上升沿,当输入参考时钟信号Ref的上升沿超前反馈信号Fed的上升沿到达鉴频鉴相器时,鉴频鉴相器的输出UP为高,而此时DOWN保持为低电平,当Fed的上升沿也到来时,输出被复位;当信号Fed的上升沿超前参考信号Ref到来时,输出DOWN为高,当Ref的上升沿也到来时,鉴频鉴相器被复位。因此,鉴频鉴相器根据输入信号相位差来驱动后级电路。比较两个输入信号的相位差,然后将其转变成两个数字信号来控制电荷泵的工作状态。在本设计中,由于参考输入频率仅为900 kHz,因而对鉴频鉴相器的工作速度要求并不高。因此,在满足低功耗要求的前提下,采用最简单的无死区鉴频鉴相器的结构。

为了避免死区,在复位路径中引入延时T。在设计延时时长时,首先应考虑鉴频鉴相器的工作频率。因为鉴频鉴相器的最高丁作频率为1/2Tdelay,Tdelay包括插入延时和鉴频鉴相器的内部延时。要求插入延时的引入不影响鉴频鉴相器的正常工作;另外需考虑当插入延时相对较长时,电荷泵的充、放电电流同时开启的时间就会变长,而电荷泵存在的失调就会在滤波器电容上引入抖动,即增加锁相环输出的杂散成分。因此,在鉴频鉴相器内部延时可忽略及充分开启电荷泵的前提下,应尽量减小失调。这里插入延时取8 ns。由于后级电荷泵电路为差分输入,因此采用传输门减少反相器的延时。

3.2 带隙基准电路

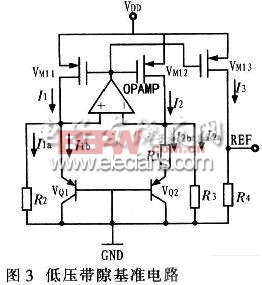

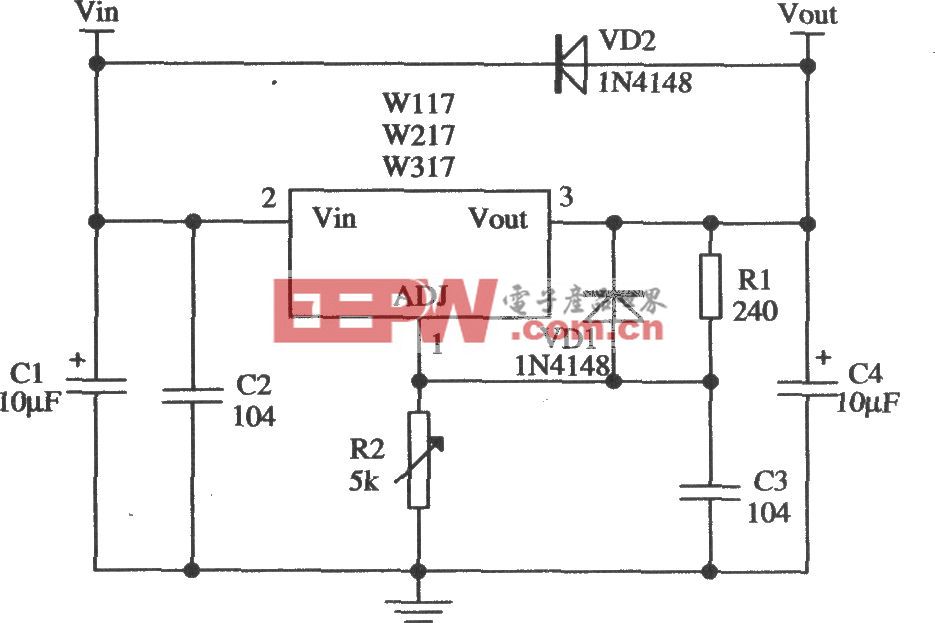

为满足带隙基准电路的低压应用,这里采用一种电流模式结构的低压带隙基准电路,如图3所示。该电路可以输出低于1 V的电压,有效降低了电路的电源电压;同时,电路中采用与电压无关的偏置及带负反馈网络的二级运放,降低了电路的电源敏感性。

基于0.35μm CMOS工艺的HSPICE仿真结果表明,该电路可工作在1.1~1.5 V的低电源电压下,并具有14 ppm/℃的低温度系数,能够输出200 mV~1.25 V的宽范围电压,并使用与电源无关偏置以及带负反馈网络的二级运放,提高输出电压的精度,该电路中,各MOS管都工作于饱和状态。电路中运算放大器采用二级结构,具有较高的低频增益。

评论