什么是逐次比较型ADC

4.特点

(1)转换速度:(n+1)Tcp.速度快。

(2)调整VREF,可改变其动态范围。

5.转换器电路举例

常用的集成逐次比较型A/D转换器有ADC0808/0809系列(8位)、AD575(10位)、AD574A(12位)等。

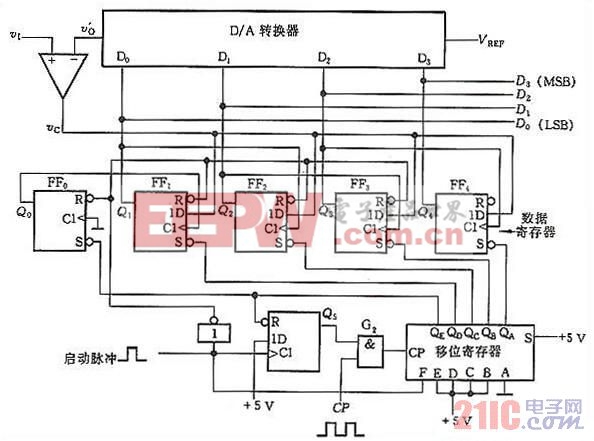

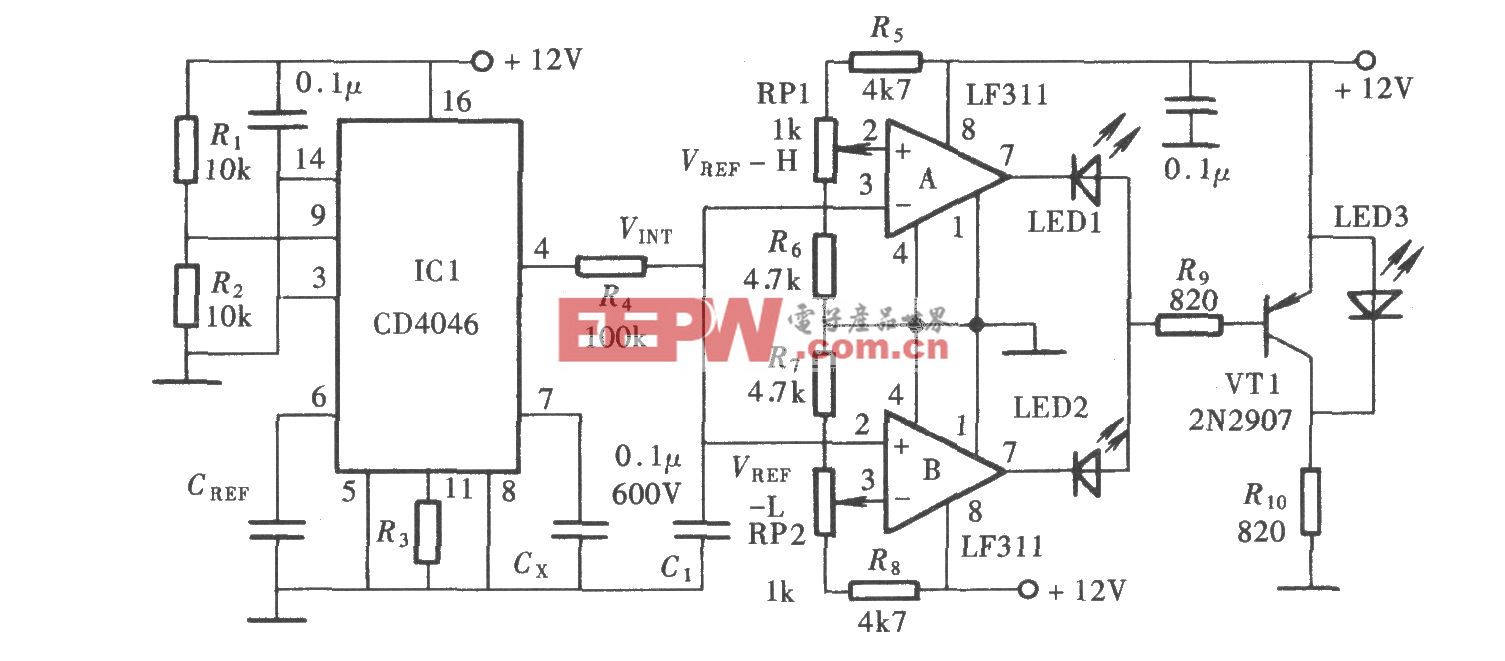

例11.10.1 4位逐次比较型A/D转换器的逻辑电路如图11.10.3所示。图中5移位寄存器可进行并入/并出或串入/串出操作,其F为并行置数端,高电平有效,S为高位串行输入。数据寄存器由D边沿触发器组成,数字量从Q4~Q1输出,试分析电路的工作原理。

图11.10.3 4位逐次比较型A/D转换器的逻辑电路

解:电路工作过程如下:

当启动脉冲上升沿到来后,FF0~FF4被清零,Q5置1,Q5的高电平开启G2门,时钟CP脉冲进入移位寄存器。在第一个CP脉冲作用下,由于移位寄存器的置数使能端F已有0变为1,并行输入数据ABCDE置入,QAQBQCQDQE=01111。QA的低电平是数据寄存器的最高位置1,即Q4Q3Q2Q1=1000。D/A转换将数字量1000转换为模拟电压vO,送入比较器C与输入模拟电压v1比较,若输入电压vI> vO,则比较器C输出vC为1,否则为0。比较结果送D4~D1。

第二个CP脉冲到来后,移位寄存器的串行输入端S为高电平,QA由0变1,同是最高位QA的0移至次高位QB。于是数据寄存器的Q3由0变1,这个正跳变作为有效触发信号加到FF4的CP端使vC的电平得以在Q4保存下来。此时,由于其他触发器无正跳变脉冲,vC的信号对它们不起作用。Q3变为1后建立了新的D/A转换器的数据,输入电压在与其输出电压vO相比较,比较结果在第三个时钟脉冲作用下存于Q3……。如此进行,直到QE由1变0,使Q5由1变0后将G2封锁,转换完毕。于是电路的输出端D3D2D1D0得到与输入电压v1成正比的数字量。由以上分析可见,逐次比较型A/D转换器完成一次转换所需的时间与其位数和时钟脉冲频率有关,位数愈少,时钟频率愈高,转换所需时间越短。这种A/D转换器具有转换速度较快,精度高的特点。

更多资讯请关注:21ic模拟频道

比较器相关文章:比较器工作原理

模数转换器相关文章:模数转换器工作原理

评论