D类放大器电路板布局指南

对于带有BTL输出的放大器来说,滤波环路面积是连接IC的走线、滤波电感和薄膜电容之间的面积(见图5)。为了减小环路面积,BTL输出滤波的走线必须相互平行且尽可能的保留一定的走线间距。但是,每个独立通道的输出走线可以不必彼此相邻。

低通滤波电容和共模滤波器件必须和电感尽可能的靠近。针对具有单端输出的放大器,DC阻塞电容必须随后放置。和扬声器相连的输出连接器必须和滤波器尽可能的紧密布局。

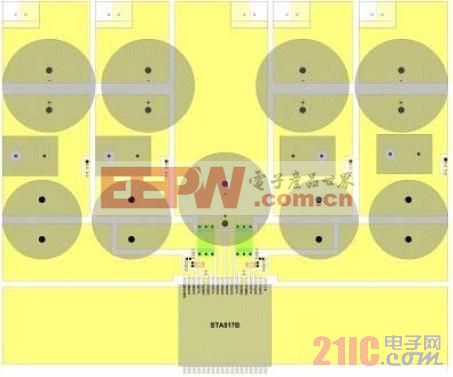

图9:四通道单端放大器输出布局示例

器件布局优先级:

1)100nF电源旁路电容

2)1uF电源旁路电容

3)缓冲器件

4)电解电容

5)输出滤波器件

100nF和1uF去耦电容必须和IC尽可能近的放置。100nF电容和IC之间的间距必须小于2毫米。为了减小走线长度和降低杂散感抗,100nF电容及其与IC的连线必须和IC在电路板的同一层。

100nF电容必须是X7R叠层陶瓷芯片电容(MLC)。1uF电容必须是钽电容或X7R叠层陶瓷芯片电容。

缓冲网络必须和IC尽可能近的布局。采用一个额定值至少100V的X7R陶瓷电容,并确保电容能够处理功率消耗。

从电解电容到IC的电源走线须采用星型连接。

电源和输出走线必须短且尽可能宽,以便降低杂散阻抗和感抗。

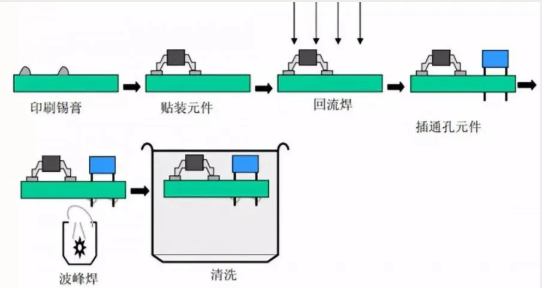

将输出信号路径紧密布线,以便减小环路面积;同时保持将滤波器件和IC尽可能近的放置。 在电路板的顶层尽可能多的布局电路,且尽力将电路板的底层作为地平面。只有在万不得已的情况下才将信号线和电源线走在电路板的底层,而且一定要灵活的使用过孔。 将放大器输入端的低电压电路远离放大器输出端的电源电路 无论何时都要尽可能的使用表贴器件。SMT器件具有更低的寄生感抗(对旁路电容性能尤为重要)

D类放大器器件需要手工布局布线,不要使用软件的自动布局布线。

总之,为了降低阻抗和感抗,处理大电流的走线如VCC和输出信号路径必须尽可能的宽且短。VCC和输出信号走线仍具有较高的电压和电流,因此这些走线必须远离敏感信号和敏感器件,如时钟信号和PLL器件。

采用一个完整的地平面。

更多资讯请关注:21ic模拟频道

评论