8位无符号数乘法运算HDL设计实例

`timescale 1 ns/ 1 ps

module mux_vlg_tst();

reg [7:0] ain;

reg [7:0] bin;

reg clk;

reg enable;

reg rst_n;

wire ready;

wire [31:0] yout;

reg[8:0] i,j;

mux i1 (

.ain(ain),

.bin(bin),

.clk(clk),

.enable(enable),

.ready(ready),

.rst_n(rst_n),

.yout(yout)

);

initial begin

$display(mux example simulation is running.n);

rst_n = 0;

clk = 0;

enable = 0;

ain = 8'hzz;

bin = 8'hzz;

#1000;

@(posedge clk);

rst_n = 1;

for(i=0;i256;i=i+1) begin (1)

for(j=0;j256;j=j+1) begin (2)

mux_ab(i,j); (3)

end

end

$display(mux example simulation is over.All right.n); (4)

$stop;

end

always #10 clk = ~clk;

task mux_ab; (5)

input[7:0] a;

input[7:0] b;

begin

@(posedge clk); #3;

ain = a;

bin = b;

enable = 1; (6)

@(posedge ready); (7)

@(posedge clk); #3;

if(a*b == yout) $display(%3d * %3d = %5d, it is right.,a,b,yout);

(8)

else begin (9)

$display(%3d * %3d = %5d, it is wrong.,a,b,yout);

$stop;

end

@(posedge clk); #3;

enable = 0; (10)

ain = 8'hzz;

bin = 8'hzz;

end

endtask

endmodule

- 乘数ain从0到255递增。

- 被乘数bin从0到255递增,以此完成全便利测试。

- 调用乘法运算任务,输入参数i和j分别会赋值给ain和bin用于运算。

- 所有测试成功完成,则最终打印“mux example simulation is over.All right.”的信息,如果测试中出现任何一个错误,则测试脚本会停止运行,也就意味着见不到这条语句。

- 产生一次乘法运算任务的激励。输入参数a和b分别为运算的输出乘数和被乘数。

- 使能信号拉高,发起一次乘法运算。

- 等待ready信号拉高,表示乘法运算完成,输出结果有效。

- 测试模块输出的乘法运算结果正确,打印相关信息。

- 测试模块输出的乘法运算结果错误,打印错误提示并停止测试脚本的运行。

- 拉低enable信号完成当前运算。

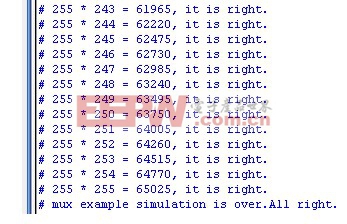

如图2所示,为当前测试结果,我们看到了最后的“mux example simulation is over.All right.”提示信息,表示测试通过。

图2 mux工程测试结果

评论