DDS的优化设计介绍

在高可靠应用领域,如果设计得当,将不会存在类似于MCU的复位不可靠和PC可能跑飞等问题。CPLD/FPGA的高可靠性还表现在,几乎可将整个系统下载于同一芯片中,实现所谓片上系统,从而大大缩小了体积,易于管理和屏蔽。所以,本文将在对DDS的基本原理进行深入理解的基础上,采用多级流水线控制技术对DDS的VHDL语言实现进行优化,同时考虑到系统设计中的异步接口的同步化设计问题,把该设计适配到Xilinx公司的最新90nm工艺的Spartan3E系列的FPGA中。

本文引用地址:http://www.eepw.com.cn/article/185570.htm1 DDS基本原理及工作过程

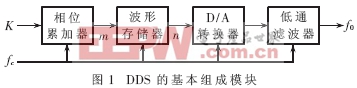

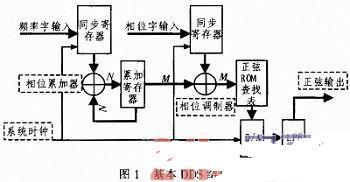

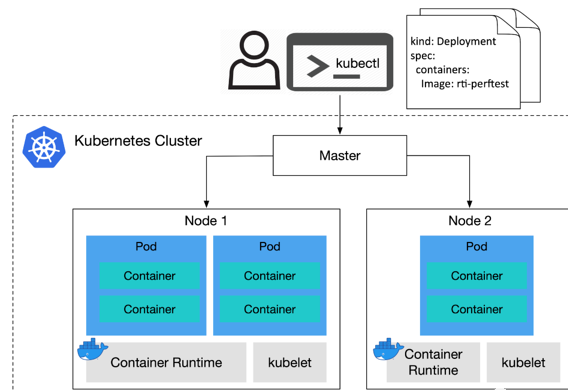

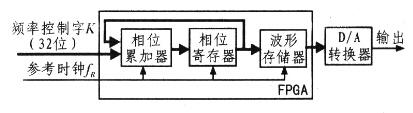

一个基本的DDS由相位累加器、波形存储器ROM、D/A转换器和低通滤波器组成,如图1所示。

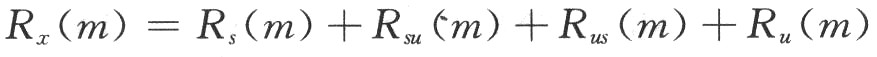

在图1中,fc为时钟频率,K为频率控制字(N位),m为ROM地址线位数,n为ROM数据线宽度(一般也为D/A转换器的位数),f0为输出频率。DDS的基本工作过程如下:每来一个时钟脉冲fc,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。其中相位累加器由N位加法器与N位累加寄存器级联构成,累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可见,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器ROM的相位取样地址,可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号,由低通滤波器滤除杂散波和谐波以后,输出一个频率为f0的正弦波。输出频率f0与时钟频率fc之间的关系满足下式:

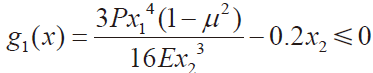

由式(1)可见,输出频率f0由fc和K共同决定,保持时钟频率一定,改变一次K值,即可合成一个新频率的正弦波。DDS的最小输出频率(频率分辨率)△f可由方程△f=f0/2N确定。可见,频率分辨率在fc固定时,取决于相位累加器的位数N。只要N足够大,理论上就可以获得足够高的频率分辨精度。另外,由采样定理,合成信号的频率不能超过时钟频率的一半,即f0≤f0/2,因此频率控制值的最大值Kmax应满足Kmax≤2N-1。

2 DDS的优化设计与实现

采用VHDL硬件描述语言实现整个电路,不仅利于设计文档的管理,而且方便了设计的修改和扩充,还可以实现在不同FPGA器件[4]之间的移植。以下采用VHDL语言,探讨对FPGA实现DDS电路的三点优化方法。

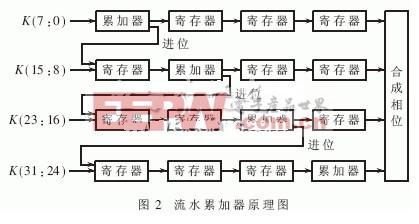

2.1 流水线累加器

在用FPGA设计DDS电路时,相位累加器是决定DDS电路性能的一个关键部分。为使输出波形具有较高的分辨率,本系统采用32位累加器。但若直接用32位加法器构成累加器,则加法器的延时会大大限制累加器的操作速度。因此,这里引入了流水线算法,即采用4个8位累加器级联结构,每级用一个8位累加器实现该部分相位相加,然后将进位值传给下一级做进一步累加。这样可大幅提高系统的工作速度。但由于累加器是一个闭环反馈电路,因此必须使用寄存器,以保证系统的同步、准确运行。具体实现如图2所示。

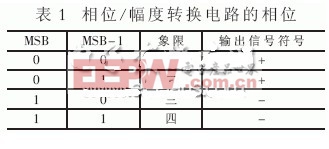

2.2 相位/幅度转换电路

相位/幅度转换电路是DDS电路中的另一个关键部分,设计中面临的主要问题就是资源的开销。该电路通常采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输入,而后通过查表和运算,ROM就能输出所需波形的量化数据。考虑到正弦函数的对称性:在[0,2π]内,正弦函数关于x=π成奇对称,在[0,π]内,关于x=π/2成轴对称。因此,在正弦查找表中只须存储相位在[0,π/2]的函数值。这样,通过一个正弦码表的前1/4周期就可以变换得到整个周期码表,节省了近3/4的资源,非常可观。具体实现如表1所示,为节省ROM资源,取相位累加器输出的高8位做为ROM的输入地址,其中最高位(MSB)控制对输出信号符号的处理,次高位(MSB-1)控制对输入地址的处理。

评论