平面磁集成EMI滤波器的等效并联电容分析

若令Gg=4Ce,Z12=1/Y12=jωL,这时电感将成为一个理想电感,绕组间的寄生耦合电容将减为零,可达到我们所期望的目标。附加电容Cg可以通过外加电容来实现,也可以利用绕组与地之间的寄生电容来实现。

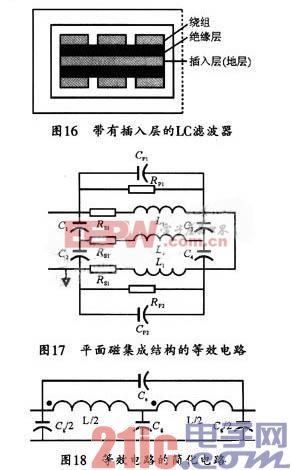

对于平面L-C磁集成结构,为得到期望的Gg,可在两绕组间加入地层,其平面结构如图16所示。设计时可采用:PlanaE43/10/28-3F和PLT43/28/4-3F3,绕组采用两层,每层3匝。绕组宽度为2mm,绝缘层厚度为0.07 mm。其等效电路如图17所示,若忽略绕组损耗和磁芯损耗,其中的L1、Cp1、Rp1t和Rs1分别为电感器第一半的电感和寄生参数;L2、Cp2、Rp2和Rs2分别为电感器另一半的参数;L3和Rs3为地层电感和电阻。忽略地层电阻时,其简化电路如图18所示。且有:

如果能满足Cg=4Ce,那么,线圈绕组间的寄生电容就可以减少至零。

4 仿真验证

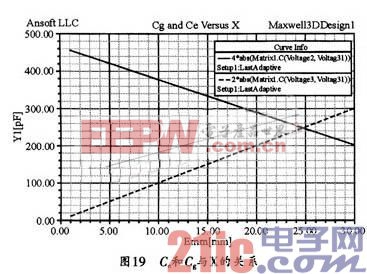

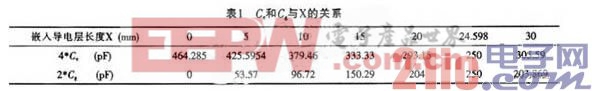

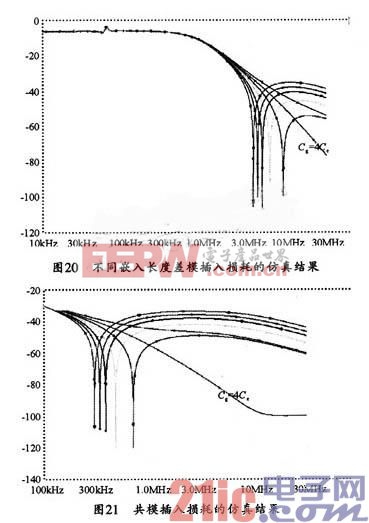

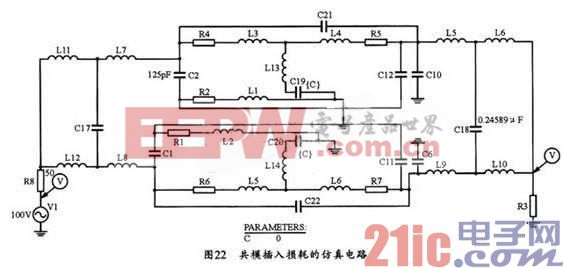

为了验证插入导电层是否能改善滤波器的高频性能,同时为了验证Ce与Cg的关系,可寻找理想的嵌入导电层长Xo之后以X为变量,得出的仿真结果如图19所示,然后再建立差模与共模仿真电路,并根据表1改变电容值Ce与Cg,所得出的差模插入损耗仿真结果如图20所示,而其共模插入损耗仿真结果如图21所示,图22为其共模插入损耗的仿真电路。

根据仿真结果可以看出,随着X不断增大,谐振点频率不断增大,在X=24.89 mm时,差模插入损耗表示出理想的状态。这时恰好Cg=4Ce。

5 结束语

仿真结果表明,嵌入导电层的滤波器可以去除EPC的影响,而且高频性能良好。滤波器的插入损耗在30 MHz以上都能达到-60 dB,并且有进一步减小的趋势。

DIY机械键盘相关社区:机械键盘DIY

EMC相关文章:EMC是什么意思

评论