精密SAR模数转换器的前端放大器和RC滤波器设计

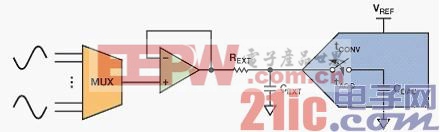

图3. 采用16位1 MSPS ADC AD7980的RC滤波器

本文引用地址:http://www.eepw.com.cn/article/185464.htm最小带宽、吞吐速率和输入频率之间的这种关系说明:输入频率越高,则要求RC带宽越高。同样,吞吐速率越高,则采集时间越短,从而提高RC带宽。采集时间对所需带宽的影响最大;如果采集时间加倍(降低吞吐速率),所需带宽将减半。此简化分析未包括二阶电荷反冲效应,它在低频时变成主要影响因素。输入频率非常低时(10 kHz,包括DC),容性DAC上建立的始终是大约100 mV的电压阶跃。此数值应作为上述分析的最小电压阶跃。

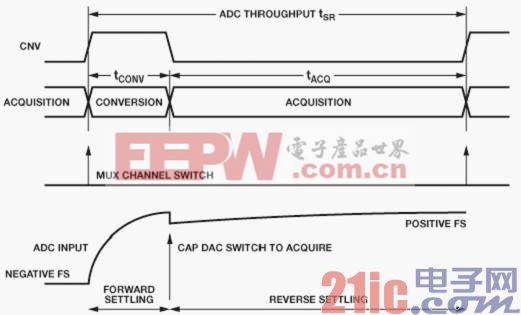

多路复用 输入信号很少是连续的,通常由不同通道切换产生的大阶跃组成。最差情况下,一个通道处于负满量程,而下一个通道则处于正满量程(见图4)。这种情况下,当多路复用器切换通道时,阶跃大小将是ADC的满量程,对于上例而言是5 V。

图4. 多路复用设置

在上例中使用多路复用输入时,线性响应所需的滤波器带宽将提高到3.93 MHz(此时阶跃大小为5 V,而非单通道时的1.115 V)。假设条件如下:多路复用器在转换开始后不久即切换(图5),放大器和RC正向建立时间足以使输入电容在采集开始前稳定下来。

图5. 多路复用时序

对于计算得到的RC带宽,可以利用表1进行检查。从表中可知,要使满量程阶跃建立至16位,需要11个时间常数(如表1)。对于计算的RC,滤波器的正向建立时间为11 × 40.49 ns = 445 ns,远少于转换时间710 ns。正向建立不需要全部发生在转换期间(容性DAC切换到输入端之前),但正向和反向建立时间之和不应超过所需的吞吐速率。对于低频输入,信号的变化率低得多,因此正向建立并不十分重要。

表1. 建立至N位分辨率所需的时间常数数目

计算出滤波器近似带宽后,就可以分别选择 REXT 和 CEXT 的值。上述计算假设 CEXT = 2.7 nF,这是数据手册所示应用电路的典型值。如果选择较大的电容,则当容性DAC切换回输入端时,对反冲的衰减幅度会更大。然而,电容越大,驱动放大器就越有可能变得不稳定,特别是给定带宽下 REXT 值较小时。如果 REXT 值太小,放大器相位裕量会降低,可能导致放大器输出发生响铃振荡或变得不稳定。对于串联 REXT较小的负载,应采用低输出阻抗的放大器来驱动。可以利用RC组合和放大器的波特图执行稳定性分析,以便验证相位裕量是否充足。最好选择1 nF至3 nF的电容值和合理的电阻值,以使驱动放大器保持稳定。此外务必使用低电压系数的电容,如NP0型,以保持低失真。

REXT 的值必须能使失真水平保持在要求的范围以内。图6显示了驱动电路电阻对失真的影响与 AD7690输入频率的函数关系。失真随着输入频率和源电阻的提高而提高。导致这种失真的原因主要是容性DAC提供的阻抗的非线性特性。

图6. 源电阻对THD的影响与输入频率的关系

低输入频率(10 kHz)可以支持较大的串联电阻值。失真还与输入信号幅度有关;对于同一失真水平,较低的幅度可以支持较高的电阻值。计算上例中的 REXT :τ = 51.16 ns,假设 CEXT 为2.7 nF,得到电阻值为18.9 Ω。这些值接近ADI数据手册应用部分给出的常见值。

此处计算的标称RC值是有用的指南,但不是最终解决方案。选择 REXT 与 CEXT 之间的适当平衡点,需要了解输入频率范围、放大器可以驱动多大的电容以及可接受的失真水平。为了优化RC值,必须利用实际的硬件进行试验,从而实现最佳性能。

选择合适的放大器

在上一部分中,我们根据输入信号和ADC吞吐速率,计算了适合ADC输入的RC带宽。接下来必须利用此信息选择合适的ADC驱动放大器。需要考虑如下方面:

· 放大器大小信号带宽

· 建立时间

· 放大器噪声特性以及对系统噪声的影响

· 失真

· 失真对于电源轨的裕量要求

该数据手册通常会给出放大器的 小信号带宽 。但是,根据输入信号的类型,大信号带宽 可能更重要,尤其是高输入频率(>100 kHz)或多路复用应用(因为电压摆幅较大),而且输入信号的正向建立更加关键。例如,ADA4841-1 的小信号带宽为80 MHz(20 mV p-p信号),但大信号带宽仅3 MHz(2 V p-p信号)。上例采用AD7980,计算的RC带宽为3.11 MHz。对于较低的输入频率,ADA4841-1是很好的选择,因为其80 MHz小信号带宽对于反向建立而言绰绰有余,但在多路复用应用中则有困难,因为对于大信号摆幅,此时的RC带宽要求提高到3.93 MHz。这种情况下,更合适的放大器是ADA4897-1,它具有30 MHz的大信号带宽。一般而言,放大器的小/大信号带宽至少应比RC带宽大两三倍,具体取决于是以反向建立还是正向建立为主。如果要求放大器级提供电压增益(这会降低可用带宽),更适用这条原则,甚至可能需要带宽更宽的放大器。

看待正向建立要求的另一种方式是查看放大器的建立时间特性,它通常是指建立到额定阶跃大小某一百分比所需的时间。对于16位到18位性能,通常要求建立到0.001%,但大多数放大器仅指定不同阶跃大小的0.1%或0.01%建立时间。因此,为了确定建立特性是否支持ADC吞吐速率,需要对这些数值进行折中。ADA4841-1针对8 V阶跃给出的0.01%建立时间为1 μs。在驱动1 MSPS(1 μs周期)AD7980的多路复用应用中,它将无法使满量程阶跃的输入及时建立,但如果降低吞吐速率,例如500 kSPS可能是可行的。

数字滤波器相关文章:数字滤波器原理

评论