正确理解时钟器件的抖动性能

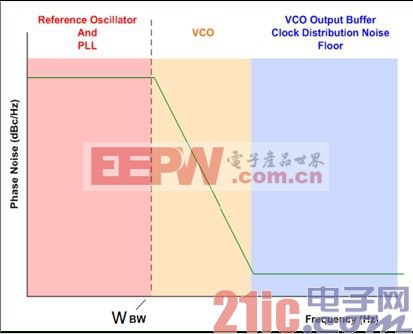

图4 典型锁相环输出噪声分布

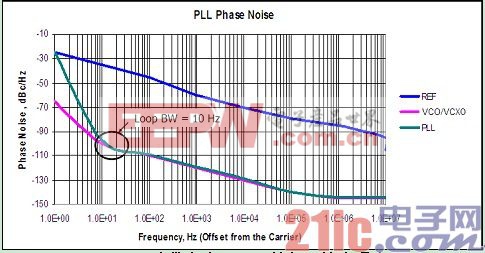

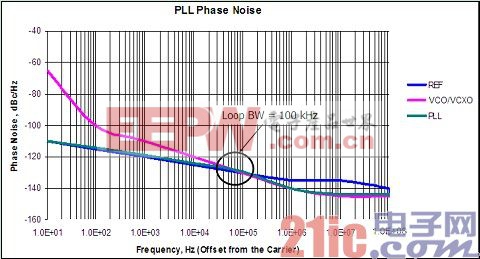

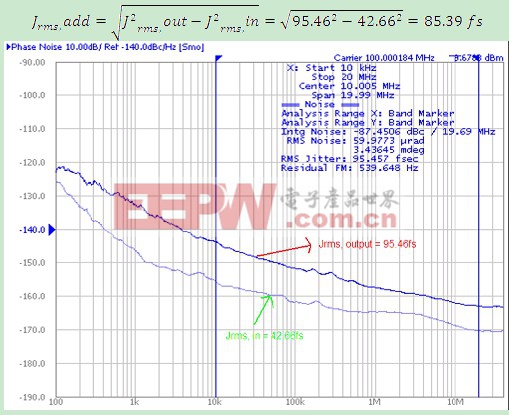

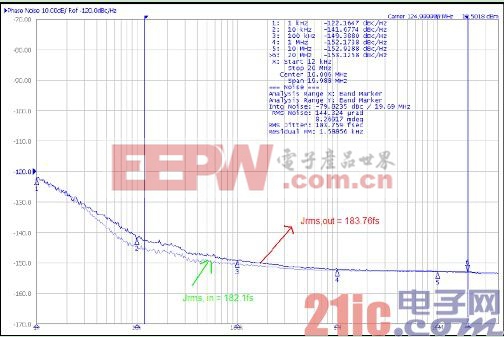

根据锁相环输出的噪声分布特性,对于基于锁相环电路设计的高抖动性能时钟器件,必须正确评估各部分电路的噪声特性,合理设计锁相环环路带宽WBW,如设计电路使得环路带宽WBW 在两噪声源相位噪声交叉点对应的频率附近,保证此时环路输出的相位噪声最小,图5 在输入参考时钟REF 有较大噪声条件下,环路带宽为~10Hz 锁相环输出噪声性能,图6 在参考时钟REF 近端噪声比较干净,环路带宽设为100KHz 附近时的输出噪声,两者在对应的应用条件下都可以得到较佳的时钟抖动性能。

图5 环路带宽为~10Hz 锁相环输出噪声

图6 环路带宽为100KHz 锁相环输出噪声

3时钟驱动器

时钟驱动器主要功能为时钟信号分发和增强驱动能力,可分为两大类:不带锁相环的高性能时钟驱动器,和带锁相环实现零延迟等功能的时钟驱动器。

3.1 不带锁相环的时钟驱动器

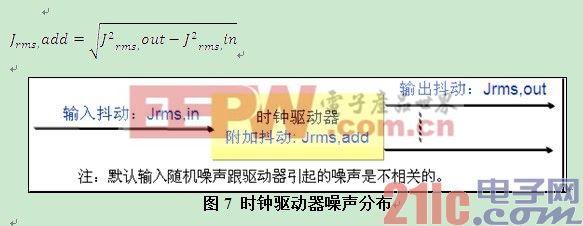

对于不带锁相环的时钟驱动器,表征抖动性能通常采用的是附加抖动指标(即噪声低噪),如下图7所示,附加抖动被定义为:

为了准确表征驱动器本身引入的抖动指标,必须要求输入均值抖动小于器件本身的附加抖动,如图8是基于CDCLVC1310 器件的一个测试例子,从图中可以看出若输入信号为100MHz 时,在1MHz 偏置频率驱动器的低噪大概为-157dBc,在(12KHz ~ 20MHz)积分带宽内对应的附加抖动指标为:

图8 附加抖动测试波形

此外,考虑在实际应用系统中,输入时钟信号抖动性能往往比不带锁相环的时钟驱动器附加抖动差,因此不同厂家采用系统级附加抖动来表征驱动器本身的附加抖动,图9 是一个例子,驱动器对输出时钟抖动贡献的系统附加抖动为Jrms, add 183.762 182.12 24.64 fs 。此时,时钟驱动器输出总抖动主要由输入信号的抖动成分决定,器件本身引入的附加抖动非常小,因此器件本身的附加抖动(或称噪声低噪)往往比系统级的附加抖动大一些,在选择高性能时钟驱动器时,要注意正确识别附加抖动和系统级附加抖动指标。

图9 系统级附加抖动测试

3.2零延迟时钟驱动器

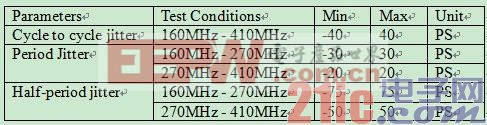

零延迟时钟驱动器主要应用在集中定时并行通信系统或基于CPU 系统的并行总线通信中,如给DDR等供时钟,要求输入和输出时钟的相位同步,采用内部集成PLL 的方法实现零延迟功能,此时器件输出的抖动性能主要由器件本身决定。对于此类器件的应用场景,必须要满足并行数据通信的建立时间和保持时间规格,因此对时钟驱动器表征抖动常用的指标是相邻周期间抖动和周期抖动,下面是CDCU2A877 器件的抖动规格,其中,考虑DDR 存储器需要上、下边沿采样,故在JEDEC 标准里对DDR 器件的半周期抖动也做了约束。

表1 CDCU2A877 器件手册抖动规格

4锁相环时钟器件

随着半导体制造工艺的迅速发展,模拟半导体行业演进到130nm或65nm 节点时,意味模拟器件的集成度可以越来越高。目前,单芯片集成锁相环时钟IC 芯片,可以实现多锁相环集成、多VCO 集成以及时钟分布电路于一体,时钟器件种类繁多,同时有些器件即可作为时钟合成器应用,也可用作抖动滤除功能实现高性能时钟输出。

4.1 时钟合成器(CSU)

也称为时钟倍频器(CMU),对输入信号进行倍频以产生各种不同频率的输出,若参考时钟为本地振荡器或内部集成时,也称为时钟发生器(Clock Generator)。根据应用场景的不同,目前集成IC 内部压控振荡器通常采用采用环形振荡器和LC 振荡器。环形振荡器的调谐范围更宽、功耗更低,而且芯片面交更小等,被大量应用在对集成度要求较高的应用场景,而LC 振荡器具有品质因数Q 值高的优势,噪声性能较环形振荡器好,被广泛引用于对抖动指标有较高要求的通信、医疗等领域。

当时钟器件作为时钟合成器应用时,环路带宽通常是在100KHz~400KHz 左右,根据具体应用场景,如输入频率和输出频率不同,环路带宽和相位余量可有差异。因此,时钟合成器输出抖动主要由参考时钟噪声分布和本地振荡器的噪声分布共同决定。作为一颗在消费类终端产品应用的时钟合成器件,CDCE706 的输出相位噪声如图8 所示,均值抖动为1.8ps@10KHz~5MHz,可满足大多数消费类产品的应用需求。.

分频器相关文章:分频器原理 锁相环相关文章:锁相环原理

评论