PSoC 5LP:带CPLD的可靠ARM嵌入式处理器

您是不是需要复杂可编程逻辑器件(CPLD)但又不愿放弃固件?或者说您希望最好在单个芯片中同时集成微控制器和CPLD?PSoC® 5LP是赛普拉斯半导体公司的最新片上可编程系统,当它用作CPU时,它就是一款32位的67 MHz ARM Cortex-M3处理器,而用作CPLD时,其可编程逻辑提供的基于LUT的FPGA门,相当于20,000多个门。

本文引用地址:http://www.eepw.com.cn/article/184727.htm高效数字架构

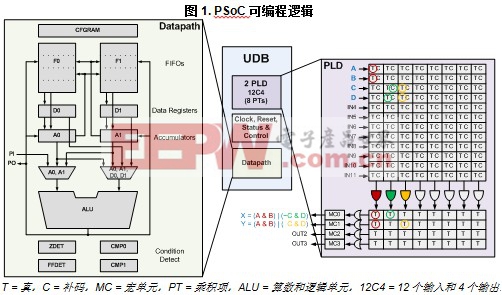

PSoC 5LP(此后简称为“PSoC”)以通用数字模块(UDB)形式提供面积效率极高的可编程逻辑(如图1所示)。UDB包含2个PLD、1个控制逻辑和1条带有数据逻辑单元的(ALU)的数据路径,每个模块都是独立而互联的。这种架构说明,任何数字功能都是由结构化逻辑(理想适用于数据路径)和随机逻辑(理想适用于PLD)组合实现的。

· PLD模块是把12个输入馈送给到8个乘积项的阵列,其输出提供给功能齐全的宏单元。

· 状态和控制逻辑提供UDB和CPU之间的无缝接口。

· 数据路径是PSoC的重要组成部分,这是一个针对通信和控制操作(如SPI或PWM所需要的)优化的8状态微微处理器。比较某些常见功能的UDB资源使用和传统CPLD/FPGA资源使用情况,保守估计每条数据路径的等效门为700多个。

· 无限互联:灵活路由对CPLD至关重要,UDB正好可实现这一点。UDB子模块可链接或路由到外设,特别是UDB的任何信号输出都能路由到任何GPIO。可能的路由组合极其丰富。

一个PSoC有多达24个UDB,因此有大量的可编程逻辑可供您使用。举例来说,您可让PSoC UDB支持24个8位PWM或8个简单UART,同时仍能支持更多逻辑。当然,UDB具有可重配置这一事实特性可让您根据自己的需求正确配置数字功能的类型和数量。

选择模式

PSoC的主要组件就是PSoC CreatorTM,这是一款免费的集成设计环境(IDE),能帮助您按照自己所想的方式开展设计。

任何数字设计都遵循如图2所示的步骤,一步步完成从要求到产品的过程。一旦明确了项目要求,就能在PSoC Creator中完成所有其它设计工作。

1. 基于组件的设计:如果您是一名固件工程师,在数字设计方面是新手,那么PSoC Creator能帮助您用熟悉的面向对象设计的方法创建出强大的数字设计。您可以将预先构建的、经过测试的“虚拟芯片”或组件拖放到设计中,创建SPI Master接口或开关去除抖动器再简单不过。此外,您还可采用经预先测试的稳健可靠的API通过C语言代码控制这些组件。一旦完成设计,PSoC Creator就能在PSoC上进行优化构建和编程。

2. 基于Verilog的设计:如果您更适应Verilog等硬件描述语言(HDL)的CPLD传统设计,那么PSoC Creator也能满足您的需求。您可编写全新的Verilog代码,将现有设计移植到PSoC UDB中,也可在设计中实例化预先构建的PSoC组件。一旦完成设计,就可让PSoC Creator进行综合,让项目对应于硬件,此外也可手动操作综合器。

万用表相关文章:万用表怎么用

c语言相关文章:c语言教程

评论