电信应用基于FPGA的功耗优化解决方案

Altera Quartus II 软件功耗优化涉及到三个步骤。首先进行“功耗预知”综合。功耗预知意味着软件可以减少每个时钟周期中要访问的RAM模块数量,还可以重新安排设计,以减少触发频率较高(或者易受干扰)的逻辑。

功耗预知综合之后,Quartus II软件对信号进行布线,减小电容,建立高功效DSP模块配置,完成功耗预知布局布线。Quartus II软件中的PowerPlay功耗优化功能指导适配器使用额外努力选项,利用专门的功耗体系结构特性,对设计进行功耗优化。使用时序约束,Quartus II软件可保证设计中的关键通路在性能上达到最优,而时序不重要的通路在功耗上最优。

发挥FPGA的优势

基于FPGA而不是代工线制造工艺进行芯片开发,可使专用芯片产品充分利用芯片制造的最新开发技术,来实现高功效解决方案。芯片供应商TPACK称这一方法为SOFTSILICON,使用Stratix IV FPGA为电信系统供应商提供运营商级以太网数据包处理、流量管理和设计包映射芯片解决方案。

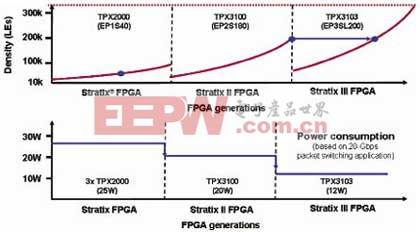

SOFTSILICON概念不但能够开发容量更大的新芯片,而且还降低了现有设计的功耗。如图1所示,TPACK的运营商级数据包引擎基于不同工艺尺寸的每一代Stratix系列FPGA,提供集成运营商级以太网数据包处理和流量管理功能。

图1 降低现有芯片解决方案的功耗

从Stratix过渡到Stratix II FPGA,TPACK将运营商级数据包引擎容量从6Gbps (TPX2000)提高到20Gbps (TPX3100),降低了1Gbps交换容量的相对功耗。通过将这一解决方案从Stratix II导入到Stratix III FPGA (TPX3103)中,功耗降低了近40%。

SOFTSILICON方法的功耗优势主要体现在以下两个方面:采用最新的FPGA平台,每Gbps以更低的相对功耗提供更大的交换容量;现有设计导入到最新的FPGA平台,进一步降低功耗。这些优势有助于满足现在以及今后运营商对低功耗的严格要求。

发挥SOFTSILICON的优势

FPGA的优势使SOFTSILICON方案受益,不仅如此,FPGA还为标准无厂模式提供其他芯片开发方法,帮助专用芯片供应商满足系统供应商和运营商的需求。

FPGA以前用于实现相对较少的功能(置入到ASSP中)或者作为“胶合逻辑”连接两片不兼容的ASSP。但是在最近几年,更多的复杂芯片方案尝试采用FPGA,TPACK就是最早这样做的公司之一。通过SOFTSILICON,TPACK提供了真正的ASSP 替代方案,具有更好的性能,特别是在功耗上。在这方面,集成也发挥了重要作用。在单芯片中集成更多的功能可以减小电路板面积,降低功耗,还可根据需要灵活更新解决方案,迅速修复故障。此外,需着重指出的是,ASSP集成的不足之处是出现故障的风险随复杂度的升高而增大,而对于FPGA来说,则可迅速纠正这些故障,降低了集成的外在风险。

评论