一种12位25MS /s采样保持电路设计

4 电路仿真及分析

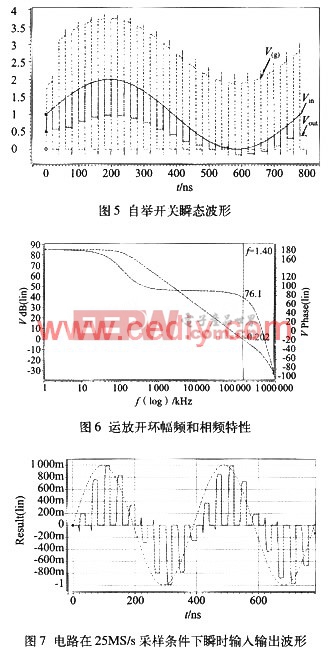

采用Hspice基于SMIC 0.25μm标准数字CMOS工艺模型对整个电路进行了仿真。首先对所设计的栅压自举开关进行仿真,在25MHz时钟条件下的瞬时波形如图5所示。输入信号为1V正弦信号,从图中可以看出开关栅压信号很好地跟随了输入信号。

同时对所设计的运放在1.5pF电容负载和2.5V单电源下,偏置电压Vcm=1.2V、Vbn=0.645V、Vbnc=1.0V、Vbpc=1.145V时,开环电压增益、相位裕度、单位增益带宽、功耗、转换速率等主要电路参数进行了模拟。图6为运放的频率响应曲线,从中可以看出运放开环增益为86dB,相位裕度为76.1°,单位增益带宽为140MHz。

输入幅度为1V、频率为2.563 476MHz的正弦波信号时,整个采样保持电路工作在25MS/s条件的瞬时仿真波形如图7所示。此时,整个电路的功耗为10.41mW。

另外,输入信号分别为2.563 476MHz幅值为1V正弦波信号时,对采样保持电路的输出波形信号进行了FFT分析,对应2048点FFT频谱图如图8所示。从频谱图中可以看出由于采用全差分结构,信号的偶次谐波失真得到了很好的抑制。对应输出信号的SFDR为75.6dB。

5 结论

本文给出了一种可以进行双采样的12位25MS/s采样保持电路,电路采用SMIC 0.25 μm标准数字CMOS工艺进行设计。仿真的结果表明,所设计的采样保持电路完全符合12位25 MS/s A/D转换器的性能要求。

评论