一种12位25MS /s采样保持电路设计

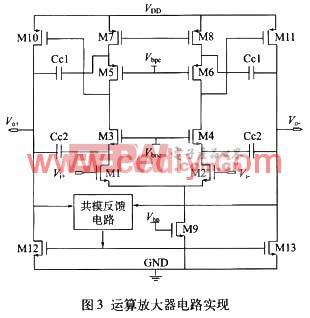

运放的第一级为“套筒式”共源共栅结构,使用NMOS管作为输入管,可以使运放的速度达到最大,因为NMOS管比PMOS管有更高的迁移率和截止频率;第二级采用共源级输出,以提供最大的摆幅和驱动能力。两级中的补偿采用米勒补偿,与一般的米勒补偿相比,采用共源共栅结构的米勒补偿更能提高单位增益带宽。

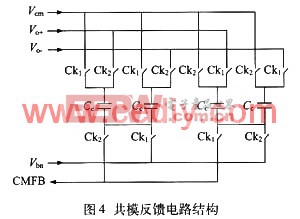

由于所选用的运算放大器电路为全差分结构,在全差分的跨导运算放大器中,为了稳定直流共模输出电压,通常采用共模反馈电路(CMFB),运放共模反馈电路结构如图4所示,电路采用开关电容结构。由于反馈电路采用无源元件(电容)和开关组成,运算放大器的输出电压不受共模检测电路的限制,并且反馈电路不消耗静态直流功耗。其中Vcm和Vbn为偏置电压,当时钟为Ck1有效时,左边两个电容组成的左半支路的电容两端分别接Vcm和Vbn复位,右半支路的两个电容工作产生共模反馈电平CMFB。当时钟为Ck2有效时相反,左半支路工作产生共模反馈电平CMFB,右半支路复位。其中4个电容取值均为0.2pF,所有开关实现均为CMOS开关。

3.3 采样电容的确定

对于12位精度的A/D转换器来说,其信噪比(SNR)应大于76dB。SNR取决于信号摆幅均方值于等效输入噪声均方值之比。本文设计采用SMIC 0.25μm标准数字CMOS工艺进行设计,电源电压为2.5V单电源,所选取的直流共模偏置为1.2V,信号摆幅为±1.5V。为达到76dB的SNR,采样电容值应大于0.5pF。为留有足够的余量,选取采样电容C5=Cf=1.5pF。

评论