简易USB与LVDS接口转换器

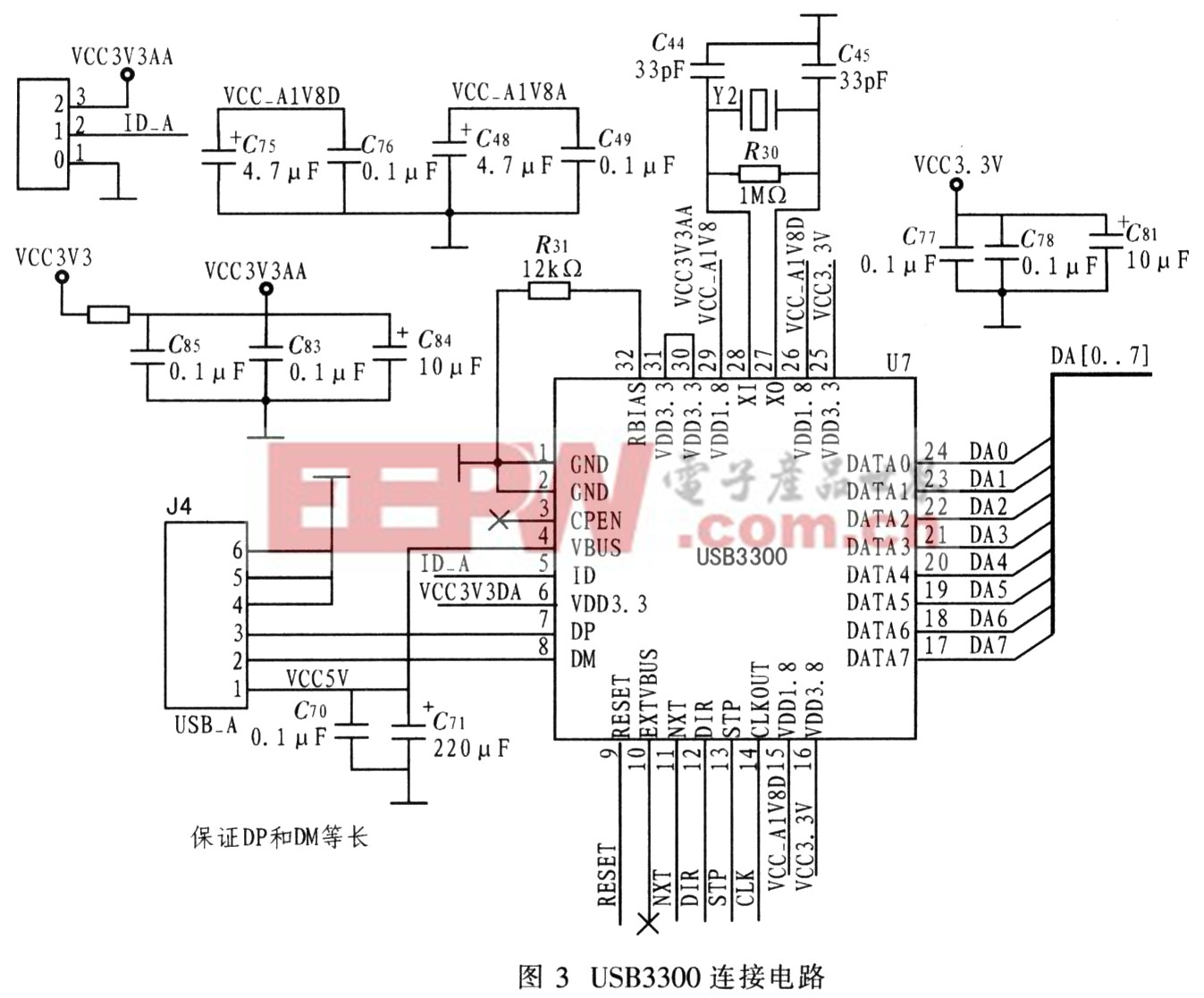

USB3300连接电路如图3所示,为控制数据传输的时序同步,采用USB3300的时钟输出工作方式。USB3300外接24 MHz的时钟晶体振荡器,经内部锁相环电路转换为60 MHz信号,通过CLK输入FPGA作为其时钟信号,从而实现FPGA与USB3300的时钟同步。USB接口部分与FPGA的数据交互传输通过双向的8 位数据信号实现,USB3300通过DIR与NXT信号输出控制数据信号的传输方向,而FPGA通过STP信号控制数据的传输方向USB3300的状态。这样便实现FPGA与USB3300的数据交互。本文引用地址:http://www.eepw.com.cn/article/181241.htm

3.3 协议数据转换部分

系统协议数据转换部分中采用现场可编程逻辑门阵列器件EP1C6U240C8进行编程,主要实现的功能是将与USB3300交互的数据转换成10位并行数据与SN65LV1023和SN65LV1224交互,同时通过STP信号控制 USB3300的数据传输方向和USB3300的状态。由于USB协议本身有低功耗模式,在低功耗模式时锁相环关闭,在硬件设计时一定要接RESET控制键,这样便于软件编程的调试。

3.4 LVDS接口电路

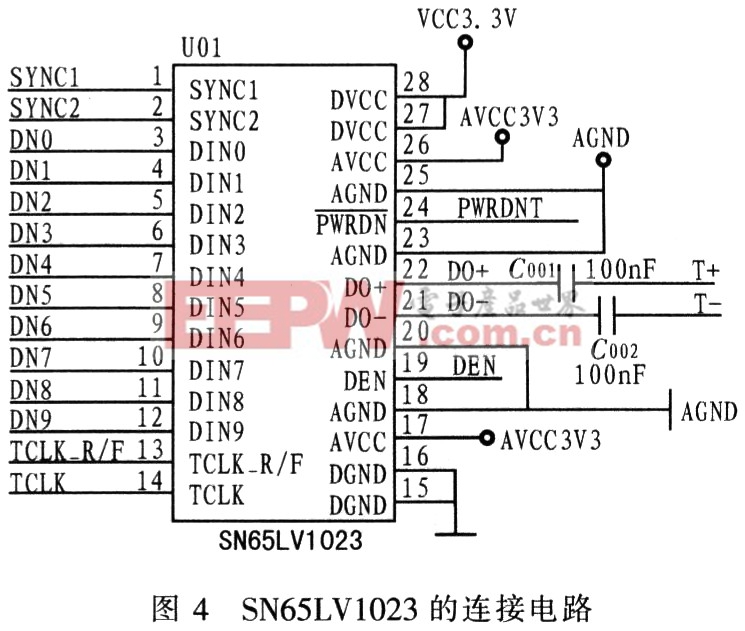

低压差分信号LVDS(Low Voltage Differential Signaling)接口是一种高速数据传输的物理层接口,其电压信号摆幅低,技术上能做到且产生极低噪声,功耗也极低,主要用于服务器、可堆垒集线器、无线基站、3FG交换机及高分辨率显示等。与USB协议接口类似其物理层信号直接与FPGA进行交互相当复杂,系统选用SN65LV1224和 SNLV1023,将FPGA与LVDS接口物理层数据交互,转换为10位的并行信号,同时通过相关的控制信号控制数据的传输方向。SN65LV1023 与SN65LV1224的硬件连接电路分别如图4和图5所示,其中SN65LV1023实现10位并行数据转换成LVDS的低压差分信号,同时FPGA通过TCLK_R/F控制内部锁相环,进而控制SN65LV1023状态。而SN65LV1224则将LVDS的低压差分信号转换成10位并行数据信号输入 FPGA,这样通过SN65LV1023与SN65LV1224,便在较为简单的情况下实现FPGA与LVDS接口的数据交互。

4 系统软件设计

利用可编程逻辑门阵列FPGA转换协议数据,由于系统使用USB3300可将USB协议物理层信号转换成8位并行信号,而使用SN65LV 1023与SN65LV1224则将低压差分信号LVDS转换成10位并行信号,这样大大简化FPGA的编程。

评论