基于0.5 μm BCD工艺的欠压锁存电路设计

3 电路仿真与分析

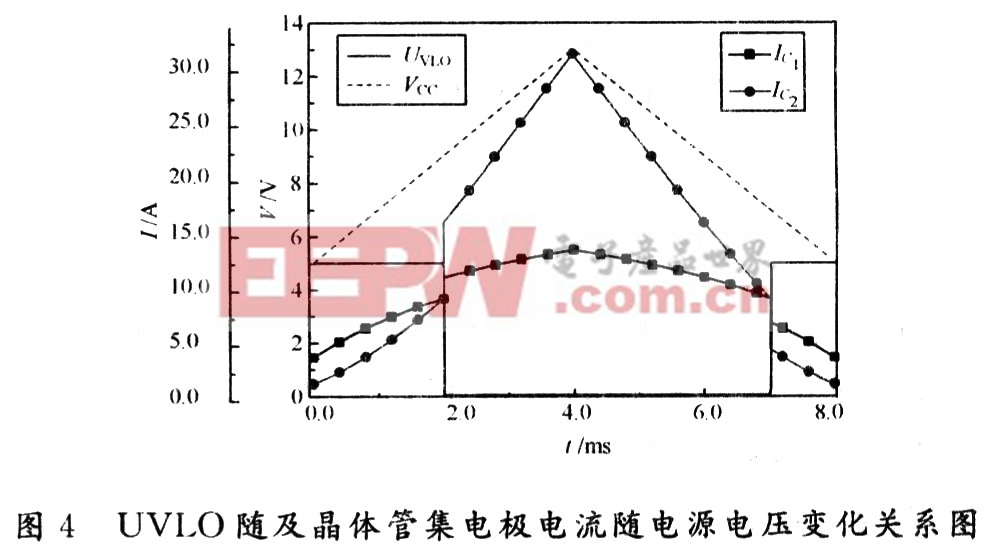

使用HSpice电路仿真软件在CSMC 0.5μm BCD工艺库下对UVLO电路进行仿真。由上面分析可知,UVLO电平翻转与晶体管Q1,Q2集电极电流变化速度快慢密切相关,所以对带隙基准晶体管上集电极电流变化做了如图4的仿真。从图4中可以明显看出,在2 ms以前,IC1>IC2,UVLO输出高电平。在2 ms时,两个晶体管的电流都急剧变大,但是由于Q2管的跨导比Q1管小,所以很快,IC1IC2,UVLO输出为低电平。下面可同理推出。

因为DC-DC芯片应用的温度范围比较大,而且工艺中的电阻、晶体管等受温度影响也比较大,所以在实际设计中,应当充分考虑到这点。在此对UVLO不同温度下进行仿真,尽可能把滞回区间的误差缩小到很小的范围内,以满足DC-DC芯片在宽温度范围内工作。表1和图5是对本文所设计的UVLO电路在-40℃,25℃,80℃和140℃下的仿真结果。从中可以看出,在25℃时,Von=9 V,Voff=7 V,滞回区间是2 V。在其他温度下的偏差最大也不超过0.2 V,可见其最突出的优势是可以在宽温度范围内工作而不失精度。

除此之外,当芯片发生欠压锁存时,芯片的功耗也是非常小的。这主要是因为当芯片发生欠压锁存时,芯片的其他部分都不工作,也就不消耗功率,UVLO电路的主要功耗是流过带隙晶体管和R3,R4,R5,R6电阻的电流所产生,只要适当地调节这些电阻阻值就可以把功耗降低到最低,但是考虑到版图的面积,实际仿真中的功耗可减小到150μW以下。

4 版图设计

使用CSMC 0.5 μm BCD工艺技术,对UVLO电路设计版图。由于利用带隙基准原理,在要求精度较高的情况下,设计时应注意UVLO模块与其他模块隔离。与传统的UVLO电路相比,最显著的提升就是版图面积大大缩小,只要工艺中包含高阻值的电阻类型,这种优势就更为突出。

5 结 语

在此针对DC-DC电源管理系统所必须的欠压所存功能,详细介绍一种新的改进UVLO电路,相对于传统的UVLO电路,它最突出的优点是不使用额外的带隙基准源和复杂的数字逻辑,因此节省了芯片面积。HSpice仿真结果表明,它在-40~+140℃范围内最大失真不超过2 %,因此可以在宽温度范围内工作。基本适用于各种类型的电源管理类芯片,对工艺要求也不高。

评论