CPCI总线在数字化电台中的设计

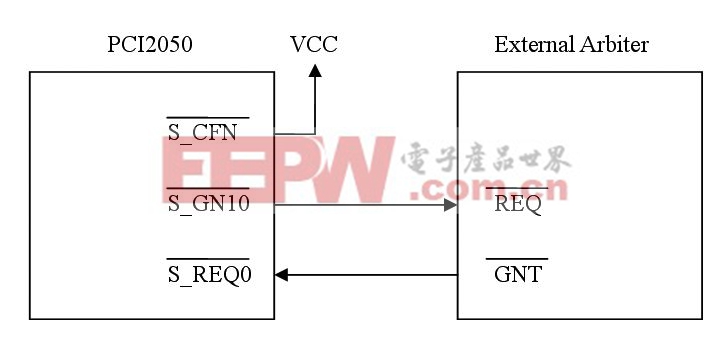

⑥ 对于二级总线的仲裁,PCI2050提供两种方式:外部总线仲裁和内部总线仲裁。S_CFN#引脚为选择引脚,当S_CFN#引脚为高时,使用外部总线仲裁器。这时,S_REQ#1~S_REQ#8和S_GNT#1~S_GNT#8引脚被置为高阻状态,外部仲裁器与PCI2050的连接方式如图2所示。

图2 PCI2050与外部仲裁器的连接

在PCI2050的内部总线仲裁模式中,S_CFN#引脚为低,PCI2050对外围卡通过S_REQ#0~S_REQ#8引脚提出的请求进行仲裁,然后通过S_GNT#0~S_GNT#8引脚和进行响应。PCI2050的S_REQ#0~S_REQ#8和S_GNT#0~S_GNT#8引脚分别与CPCI规范定义的CPCI J1、J2的相应引脚经过串接端接电阻和上拉后连接。

5 芯片工作模式的选择

PCI2050可以选择工作在三种不同的工作模式下:TI CPCI热插拔模式、TI电源管理模式和与Intel 21150兼容模式。选择引脚分别为:MS0、MS1,模式选择定义如表2所示。

TI CPCI热插拔模式支持CPCI热插拔,满足CPCI电源管理接口规范1.1版本;TI电源管理模式不支持CPCI热插拔,只满足CPCI电源管理接口规范1.1版本;与Intel 21150兼容模式也不支持CPCI热插拔,且只满足CPCI电源管理接口规范1.0版本。根据CPCI总线应用设计的需要,可以选择TI CPCI热插拔工作模式。

当PCI2050选择工作在TI CPCI工作模式下时,为了确保热插拔逻辑的正常工作,要求必须将PCI2050的HS_SWITCH/GPIO3和HSENUM#引脚上拉。同时,由于没有使用PCI2050的关于GPIO的引脚,且因为这些引脚在缺省条件下定义为输入脚,为了避免误触发,应该将这些引脚全部上拉。

6 芯片内部寄存器设置

PCI2050桥接芯片作为一个独立功能的PCI器件,具有和所有PCI设备一样的配置空间,并且作为PCI桥,它遵守PCI-to-PCI桥规范1.1所定义的PCI配置空间。PCI2050除了具有标准的PCI-to-PCI桥规范定义的配置空间外,还具有TI特有的寄存器组(40h-FFh)。这些寄存器组包含PCI2050某些特有功能的控制位,在PCI2050的应用中起特殊控制作用。但在本设计中,根据系统实际应用需求,对PCI2050的内部寄存器不需要进行特别操作,可以使用其缺省值。

结论

基于PCI2050桥接芯片的CPCI总线设计在数字化短波电台中的应用比较稳定可靠,为数字化短波电台提供了丰富的可插拔插槽。CPCI总线的标准化规范也为数字化短波电台的模块化设计和功能扩展提供了便利,并且还极大地提高了电台的可操作性、维修性和保障性,使数字化短波电台能更好地适应各种复杂的应用环境。

评论