CPCI总线在数字化电台中的设计

1 桥接芯片的选择

PCI桥接芯片尽管可以使用FPGA通过硬件编程语言来实现,但由于PCI总线规范自身的复杂性,要想在短期内做到性能优化和操作稳定,难度很大。而现在市场上有许多厂家提供了很多成熟的产品,根据系统集成的特性,我们选择TI公司的PCI-to-PCI桥接芯片PCI2050。 本文引用地址:http://www.eepw.com.cn/article/181072.htm

PCI2050属于透明PCI-to-PCI桥,提供了两条PCI总线间的高性能连接,实现一条PCI总线的主设备和另外一条PCI总线的从设备间的传输,兼容Intel 21150。PCI2050桥符合PCI局部总线规范2.2,并可用于PCI总线的扩展,提供支持9个设备的可编程2优先级总线仲裁器;一次侧和二次侧都支持33MHz时钟、32位扩展信号。PCI2050提供CPCI热插拔能力,可完美解决多功能CPCI卡和单功能CPCI的热插拔问题。PCI2050桥符合PCI-to-PCI Bridge Specification1.1,符合PCI电源管理规范1.0/1.1。

2 电源和地的连接

PCI2050使用的核心工作电压为+3.3V,CPCI标准机箱的底板上通过J1连接器提供满足要求的+3.3V电压,在使用时无须DC/DC转换。但根据标准设计规范,在PCI2050的电源引脚附近需要设置旁路电容。所以在印制电路板布线时,在PCI2050的所有电源引脚附近需要设置一个0.1μF的陶瓷电容器作为旁路电容。

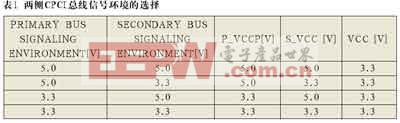

PCI2050在两侧总线方向都支持+5V和+3.3V信号环境,它们的选择是通过对P_VCC和S_VCC引脚施加不同的电压来实现的,详细的选择方式如表1所示。

由于PCI总线为高速总线,为了避免电源和地的干扰,在印制板布线时采取单独的电源层和地层布线。但因为在设计过程中使用了+5V和+3.3V两种电源,所以在同一电源层上又为+5V和+3.3V两部分分开铺铜。

3 PCI总线一次侧的连接

数字化短波电台的嵌入式计算机模块提供了符合PCI总线规范的标准PCI信号接口,这些信号与PCI2050的第一级总线侧的信号定义完全兼容,在设计时可以将嵌入式计算机的PCI信号输出直接连接到PCI2050一次侧的相应引脚。在初始化配置空间读写时,PCI2050作为上一级PCI总线的操作对象,提供了IDSEL引脚进行器件选择,按照PCI2050使用手册,该引脚可以连接到高24位PCI总线中的任意一根。同时,为了减低地址线的容性负载,需要在该信号连线上串接一个1kΩ的电阻。

在CPCI总线设计中,将PCI2050的IDSEL引脚通过1kΩ电阻连接到了AD19引脚。同样,PCI2050在二级总线侧可以支持9个PCI器件,对于每个二级总线侧的PCI器件的IDSEL引脚,也可以经过1kΩ电阻连接到PCI2050的S_AD31-S_AD16引脚中的任意一根。

评论