高速电路设计中信号完整性分析

在高速电路设计中,对信号布线存在的另一个共性问题。如果没有特别的原因,应该尽可能消除所有的短接线。在高频率电路设计中,短接线就如同由于信号线的阻抗匹配而引发的辐射一样。

在高速电路设计的布线中特别需要注意差分对的布线。差分对是通过两条完全互补信号线驱动的。差分对可以很好的避免噪声干扰和改进S/N率。然而差分对信号线对布线有特别高的要求:

1、两条线必须尽可能靠近布线;

2、两条线必须长度完全一致;

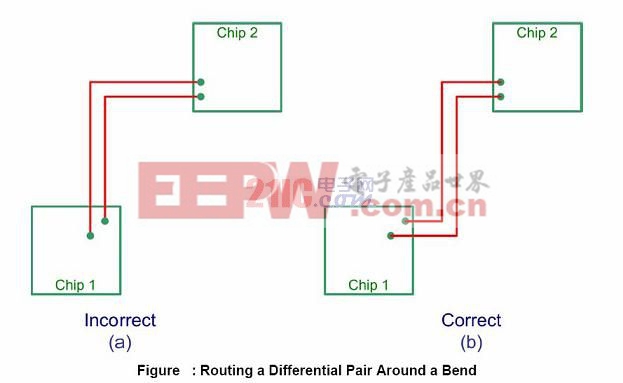

在两个没排列在一起的器件间布差分对信号线如何合理的布线是一个关键问题。

上图a中由于两条信号线的长度不一致,将会出现一些不确定风险。正确的布线应采取上图b中的方式。在差分对布线中的通用规则是:保持两条信号线同等间距并相互靠近。

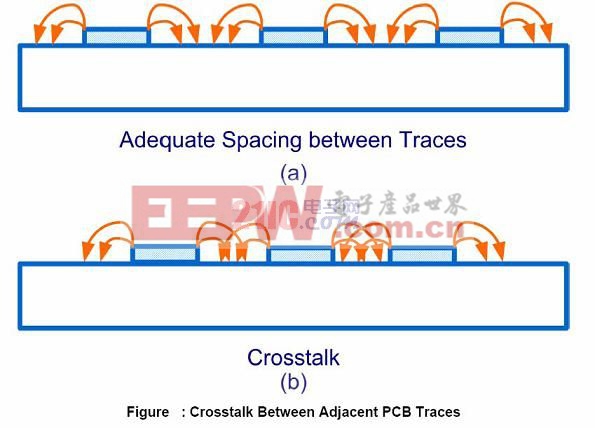

5、串扰

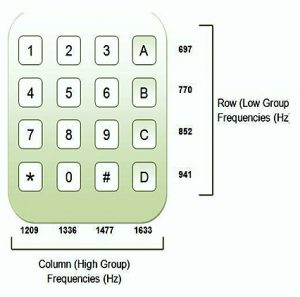

在PCB设计中,串扰问题是另一个值得关注的问题。下图中显示出在一个PCB中相邻的三对并排信号线间的串扰区域及关联的电磁区。当信号线间的间隔太小时,信号线间的电磁区将相互影响,从而导致信号的恶化,这就是串扰。

电度表相关文章:电度表原理

评论