升压型DC-DC变换器电流环路补偿设计

2.2 电流采样原理与方法

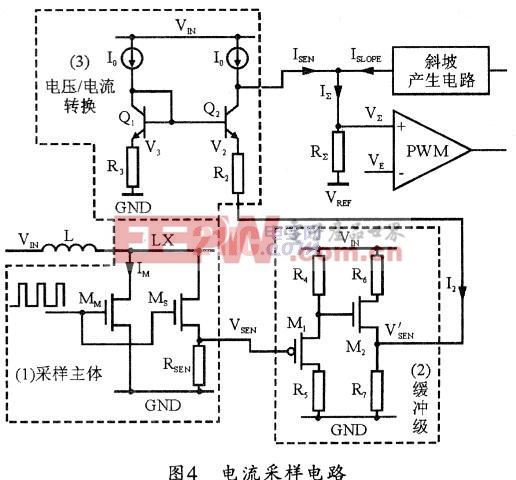

传统电流采样方法是在开关管的电流通路上串接检测电阻,这样不仅降低了DC-DC转换器的效率,而且对于传统工艺来说,制作这样的小电阻也很困难。为了弥补这些不足,本文在SENSEFET采样方法的基础上,加入了简洁的V/I变换电路,从而形成了一种结构简单且精度较高的采样电路,其电路主体如图l中的采样电路所示。其中MM为POWER FET,其宽长比设计的非常大,可以减小其导通阻抗(本电路的典型值为150 mΩ);Ms为SENSE FET;检测电阻RSEN可利用工作在线性区MOS管的导通阻抗特性,使其宽长比与Ms相同,因此,导通阻抗与Ms的相等,记为RSEN。为了减小采样损耗,一般必须使(W/L)MM(W/L)Ms。

设(W/L)Ms:(W/L)MM=n(n的取值一般不低于100),开关管电流为IM,则有:

采样电压VSEN经过简洁实用的V/I转换电路后,可将其转换成所需要的采样电流信号ISEN,然后与斜坡电流信号ISLOPE在R∑进行叠加,就可得到所需的电压V∑。本文引用地址:http://www.eepw.com.cn/article/180962.htm

3 改进型电路设计

3.1 斜坡产生电路

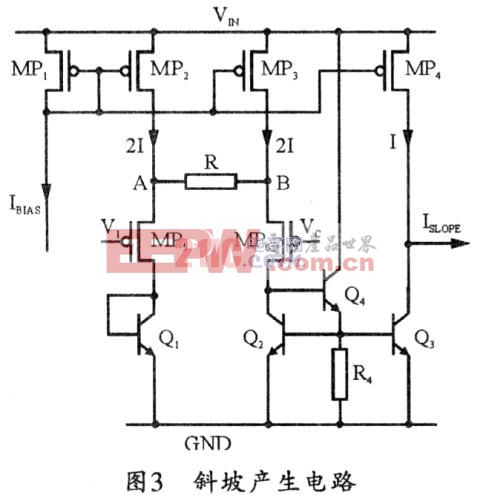

图3所示是一种改进型斜坡产生电路,图中,MP5、MP6为匹配的差分对管:Q1、Q2匹配(rCE(Q1)=rCE(Q2),为负载管,它们的发射极面积相等,为Q3的两倍。负载管Q1、Q2采用三极管,可在高匹配性的同时大大减小噪声影响。在Q2的集电极与基极之间加一个射极输出的晶体管Q4,可以减小Q2和Q3基极电流对ID(MP6)的分流;而在Q2和Q3的基极与地之间加电阻R4,则可用来提高Q4的β。Vc为片内振荡器充放电电容上的锯齿波电压,Vc的变化范围为V1-V2。其中V2和V1分别为振荡器充放电的高、低设定电压值。

此电路主要任务是将电容上的锯齿波电压转换成所需要的斜坡电流。

3.2电流采样电路

图4所示为本系统中的电流采样电路。该电流采样电路由三部分组成:采样电路、缓冲级电路和电压/电流(V/I)转换电路。其中采样电路采样得到反映电感电流的电压VSEN后,可经过优化处理的缓冲级电路进行电平平移,从而得到VSEN’,以避免采样电压受到后级电路的影响,即:

最后,VSEN’经过V/I转换电路,就可以转换成所需要的电流信号ISEN,以便和ISLOPE进行叠加。

基尔霍夫电流相关文章:基尔霍夫电流定律

评论