开关电流电路延迟线的设计

3.2 传输误差的改善

传输误差产生的原因是当电路级联时,因为传输的是电流信号,要想信号完全传输到下一级,必须做到输出阻抗无穷大,但在实际中是不可能实现的,只能尽可能地增加输出阻抗。

计算出输出电阻为:

与第二代基本存储单元相比,输出电阻增大

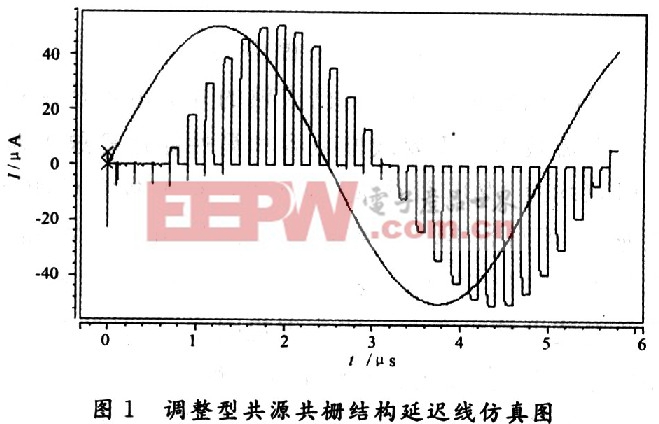

采用O.5μm CMOS工艺,level 49 CMOS模型对电路仿真,仿真参数如下:

所有NMOS衬底接地,所有PMOS衬底接电源,所有开关管宽长比均为0.5μm/O.5 μm。输入信号为振幅50μA,频率为200 kHz的正弦信号,时钟频率为5 MHz,Vref=2.4 V,VDD=5 V。表1中给出了主要晶体管仿真参数。

将原电路按照延迟线的结构连接并仿真,延迟3个时钟周期(相当于6个基本存储单元级联),仿真结果如图l所示。

4 结语

详细分析了第二代开关电流存储单元存在的缺点,提出了改进方法,并设计了可以延迟任意时钟周期的延迟线电路,仿真结果表明,该电路具有极高的精度,从而使该电路能应用于实际当中。其Z域传输函数为![]() ,在实际应用中,该电路可作为离散时间系统的基本单元电路。

,在实际应用中,该电路可作为离散时间系统的基本单元电路。

由于开关电流技术具有与标准数字CMOS工艺兼容的特点,整个电路均由MOS管构成,这一技术在以后的数模混合集成电路中将有广阔的发展前景。

DIY机械键盘相关社区:机械键盘DIY

基尔霍夫电流相关文章:基尔霍夫电流定律

评论