用于SD卡的NAND flash控制芯片的设计

当需要更新数据时,写入的策略可分为两种情况。首先,当子块仍然有空闲页时,可直接将数据写到子块中的下一个空闲页中,并在spare区中记录该块对应的子块、该物理块对应的逻辑块以及该物理页对应的逻辑页,这样,当重新上电时,就可以建立逻辑物理映射关系。其次,当母块和子块都写满时,需要从空块池中取出一个新的子块。如果允许一个逻辑块对应三个或更多的物理块,一方面管理起来比较复杂,另外也会造成空物理块紧缺,因此,可以考虑将母块或者子块释放掉,这样,母块或者子块中原有的有效数据就需要搬移到新子块中并将该母块或子块擦除再释放到空块池。出于速度的考虑,选择母块和子块有效页数较少的块进行数据转移并释放。

实践证明,这样操作对写文件速度有明显提高,特别是写小文件时,其速度提升可达9.2倍。

2.3 SPARE区和ECC校验

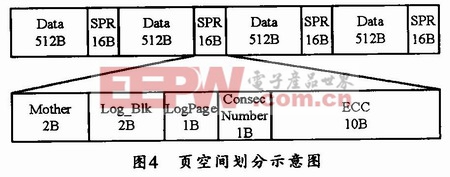

Flash中每个页里的每个字节都是没有任何差别的,物理上并没有data区和spare区的区别,具体怎样划分data区和spare区,可由用户自己决定。本设计采用的划分办法如图4所示,这样,每个扇区和一个spare区相连,故可方便连续读出,并进行校验纠错。

图4中同时给出了Spare的区定义,其中两字节用于标识本物理块所对应的母块;两字节用于标识本物理块对应的逻辑块;一字节用于标识本物理页对应的逻辑页,一字节用于标识连续逻辑页数(表示上面连续逻辑页的个数,此域可以辅助加快建立页映射表的时间),余下的10字节用于存放ECC,这样可以达到4字节错误的纠错能力。一般情况下,前面的4个字节是建立块地址映射表的关键,其次,后面两个字节则是建立页地址映射表的关键。

2.4 页映射表建立时间的优化

因为建立页映射表需要读取母块和子块中各物理页spare区以判定该物理页对应的逻辑页,而每个物理页的读取都要花费大约50μs的时间。因此,如果对每个物理页都读取,建立页映射表就会比较费时。为了加快建立页映射表的速度,一般只希望能读取一个物理页,而免于读取其他若干页,以便加快建表速度。因为很多时候都是连续写,而连续的几个物理页在逻辑上也是连续的,因此可以考虑在spare区加入连续逻辑页号,这样,重新建表时,就可根据连续页号知道连续几个物理页对应的逻辑页,从而加快建表的速度。对于最佳情形,有时只需要读一个页就可以建立整个逻辑块的页映射表。图5所示是一种加快建表的示意图。

2.5 分区

不同的flash,块数是不同的,其块映射表需要的RAM空间也不一样。对于当前主流flash,有的具有8192个块,如果对整个flash建表,需要的RAM空间将多达32KB,这样芯片成本就会比较高。一个可行的解决办法是对flash分区,比如1024个块为一个分区,每次只对一个分区进行建表,这样,RAM空间就可以降低到4KB。这样,随着将来flash容量的增加,块数即使再多,也能够用同样的方法处理,而不用增大RAM。

3 结束语

本文介绍了一种针对MLC flash的优异管理算法及软件实现方法,并且已在SD卡上大规模商用。该算法只需简单配置就能支持市场上的各种flash,而且也兼容各种SD设备。同时RAM空间需求小,成本低,寿命长,兼容性好,扩展性强,flash空间利用率高,具有很高的商用价值。

评论