变压器绕制工艺之变压器分布电容

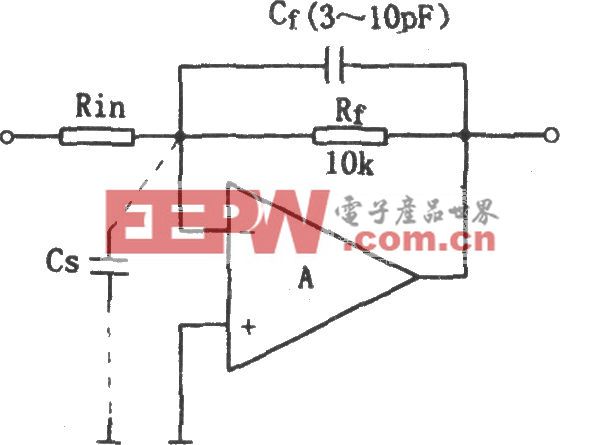

层间电容是变压器的分布电容中对电路影响最重要的因素,因为这个电容会跟漏感在MOSFET开通于关闭的时候,产生振荡,从而加大MOSFET与次级Diode的电压应力,使EMC变差。

既然有害处,那么我们就需要想办法来克服它,把它的影响降低到可以接受的范围。

方法一:参照6楼的公式,在d上作文章,增大绕组的距离来减小层间电容,最有代表性的就是采用三重绝缘线。

但这个方法有缺点,因为线的外径粗了之后,带来的后果就是绕线层数的增加,而这不是我们想看到的。

方法二:可以通过选择绕线窗口比较宽的磁芯骨架,因为绕线窗口宽,那么单层绕线可以绕更多的匝数,也意味着可以有效降低绕线的层数,那么层间电容就有效降低了。

这个是最直接的,也是最有效的。

但同样有缺点,选择磁芯骨架要受到电源结构尺寸的限制。

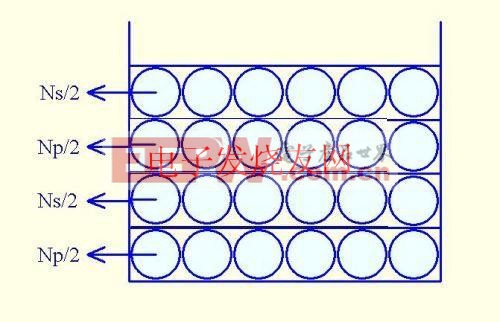

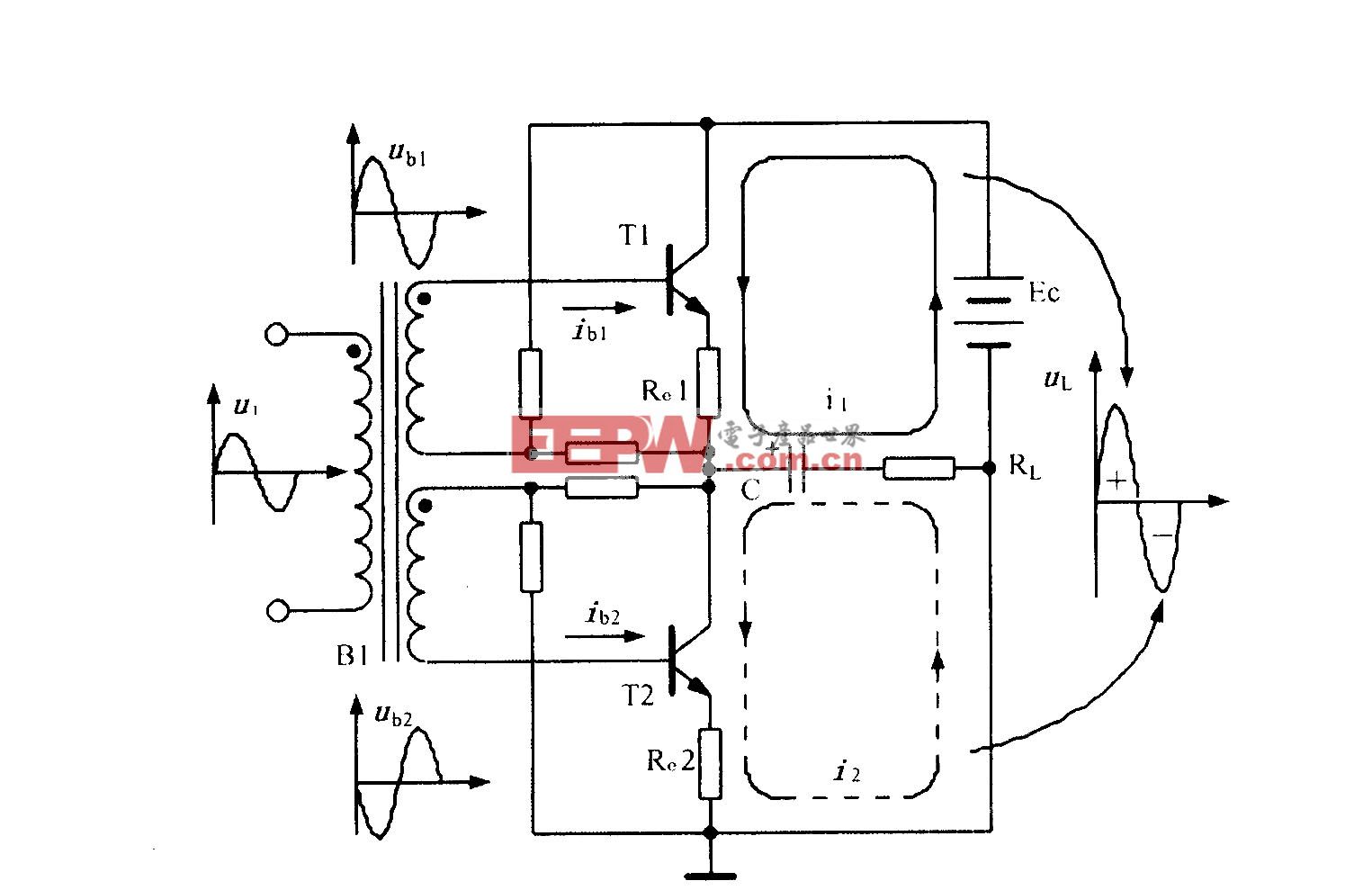

可以采用交叉堆叠绕法来降低层间电容,如下图

此种绕法有个显著缺点,会增加初次级之间的耦合面积,也就是说会加大初次级绕组之间的电容,使EMC变差,有点得不偿失的感觉。

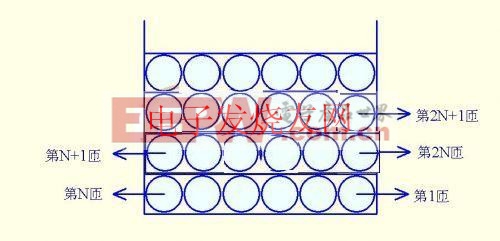

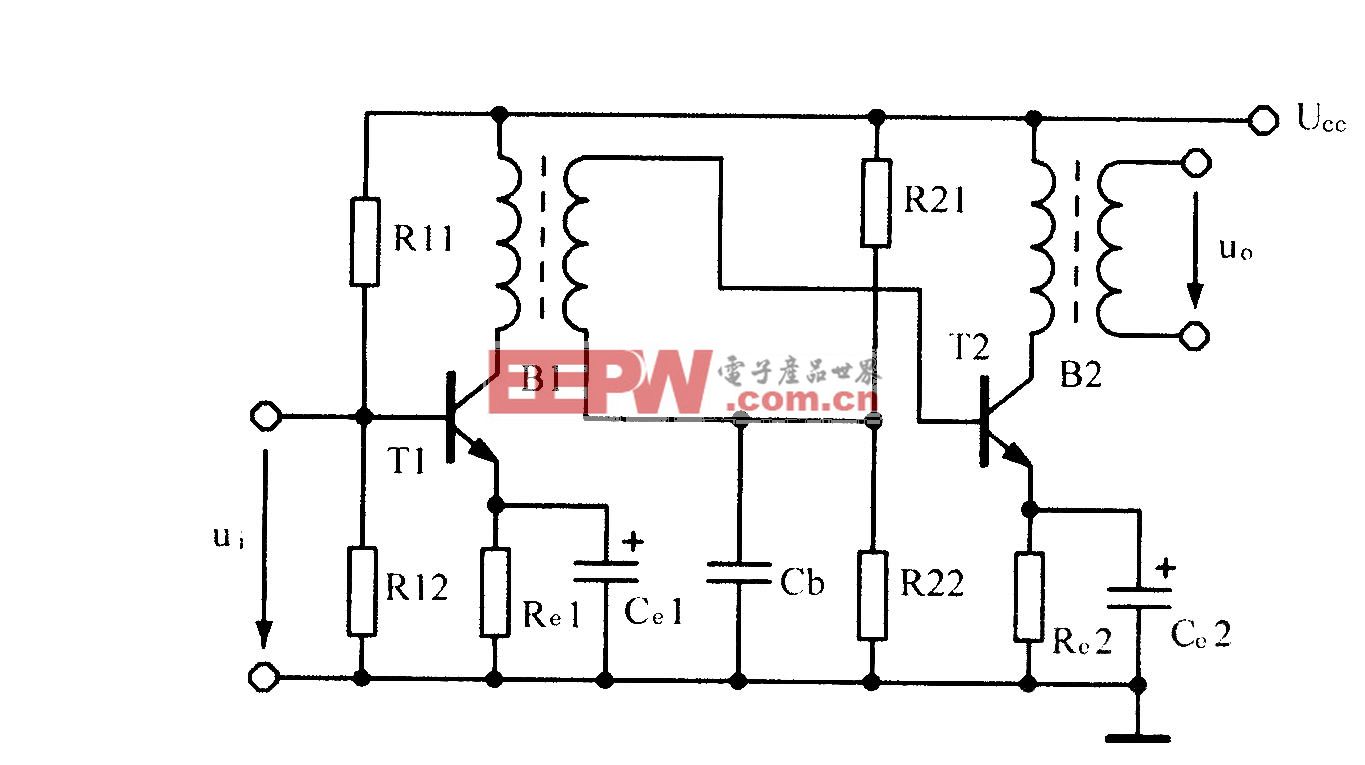

方法四:还是在绕制工艺上作文章

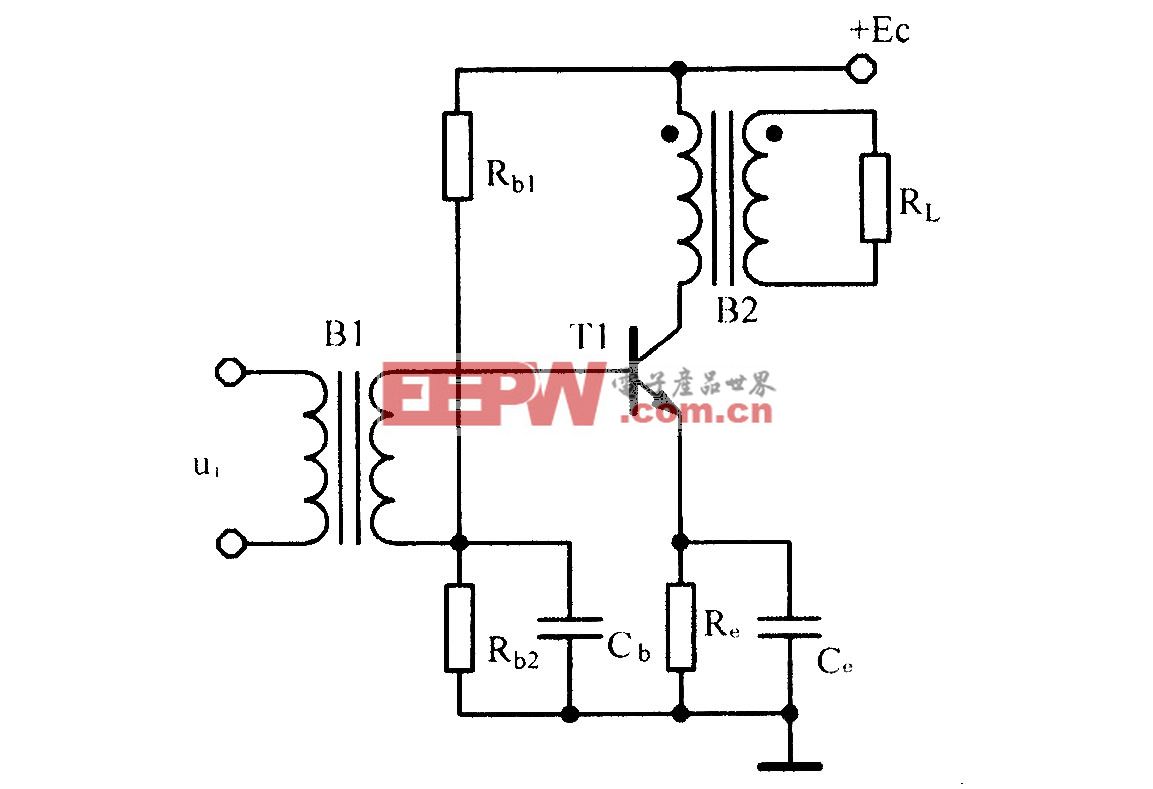

先来看普通的绕法

评论