一种基于CPLD的QDPSK调制解调电路设计

2.3 利用CPLD设计的QDPSK调制解调电路

将设计的QDPSK调制电路“qdpskb”组件和解调电路“qdpsky”组件连接在一起,为了仿真实验方便,信码数据输入采用四级伪随机码电路——从MAX+PLUSⅡ器件库中调用4个D触发器、2个异或门和1个四或非门,解调电路中位定时恢复电路产生的数据时钟直接采用qdpsk调制电路数据时钟,调制解调电路直接相连,组成的QDPSK调制解调电路如图5所示。本文引用地址:http://www.eepw.com.cn/article/179912.htm

QDPSK调制解调电路的引脚关系为:引脚clk表示数据时钟输入,引脚k1表示数据时钟clk的八分频输出,引脚data表示四级伪随机码电路数据输出,引脚c0、c1、c2、c3表示四相载波。引脚p1和p2表示信码数据data在时钟的作用下串并转换后的输出,引脚cx和cy表示差分编码后的输出,引脚qdpsk表示四相差分移相键控信号输出。引脚qx和qy表示四相差分移相键控信号的相干解调输出,引脚x和y表示差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

3 实验结果

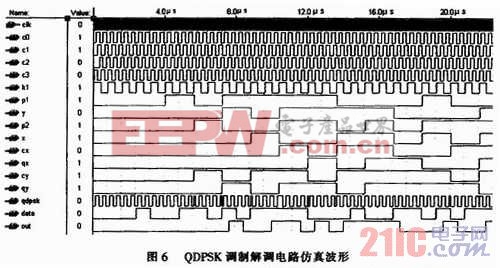

利用MAX+PLUSⅡ开发工具建立波形输入文件,在File菜单里面选择New打开新建文件类型对话框,选择Waveform Editor File项,单击“OK”。在波形编辑器窗口的Name下单击鼠标右键,出现浮动的菜单,选择Enter Nodesfrom SNF…可以打开“从SNF文件输入观测点”的对话框。在Type区选择Input和Output,在默认的情况下是打开的,单击“List”按钮,可在Available Nodes&Groups区看到设计文件中使用的输入/输出信号,单击“=>”按钮可以将这些信号选择到Selected N0des&Groups区。单击“OK”按钮,关闭对话框即可看到波形编辑窗口,将此波形文件保存为默认名。在波形文件中添加输入/输出信号名后,就可以开始对输入信号建立波形了。QDPSK调制解调电路仿真波形如图6所示。

图6中“clk”表示输入时钟,“c0”、“c1”、“c2”、“c3”表示四相载波.“k1”表示数据时钟clk的八分频输出,“data”表示

四级伪随机码电路数据输出,“p1”、“p2”表示信码数据data串并转换后的输出,“cx”、“cy”表示信码数据串并转换后差分编码的输出,“qdpsk”表示输入的信码数据四相差分移相键控信号输出。“qx”、“qy”表示四相差分移相键控信号的相干解调输出,“x”、“y”表示相干解调输出后差分译码输出,“out”表示信码差分译码后经并串转换恢复的信码数据输出。

仿真结果表明:QDPSK调制电路能正确选相,解调电路输出数据在延时约5.2μs后,与QDPSK调制输入数据完全一致。

将综合后生成的网表文件通过ByteBlaste下载电缆,以在线配置的方式下载到CPLD器件EPM7128SLC84-15中,从而完成了器件的编程。上电后,在输入端加入数据时钟,用数字存储示波器测试调制解调电路输出,实测结果完全正确,表明达到了设计要求。

4 结论

本文利用CPLD器件,设计出的QDPSK调制解调电路,利用了EDA技术中的MAX+PLUSⅡ作为开发工具,将设计的电路图综合成网表文件写入其中,制成ASIC芯片。其突出优点是自顶向下设计,查找和修改错误方便,同时先仿真,正确后再下载测试并应用,具有较大的灵活性;调制和解调放在一块芯片上,集成度非常高;解调电路输出数据延时约5.2μs,数据速率快。本文提出的QDPSK调制解调电路,已应用于小型数据传输系统中。

评论